Lot of precision low-noise amplifiers are based around composite designs are using FET input stages to obtain lowest possible noise.

Here is one of such circuits, with dual JFET on the input stage, infamous Linear Systems LSK389.

But often high-performance JFETs are hard to buy for hobby-level experimenting, so alternative tinkerer would be considering to use available FETs and do matching and selecting of the suitable samples by hand. However question arise, which parameters would be the priority for selection in low-noise high-gain amplifier application, like this one?

This topic wasn't covered much in details so far, perhaps we can discuss criteria's and methodology behind picking FETs?

To support the claims, I'd like to donate number of hours into testing and defining somewhat useful toolkit, to perform such selection easier for the community.

In the end this may result in open-source python app, that would talk to GPIB instruments to perform the required tests automagically and give a report "FET A matching to FET B within x.x %". Typical instruments for the task are SMUs, so I can support stuff like Keithley 2400 series, which many of nuts here already have. For initial tests I'll however use

Agilent 4142B with four SMUs, so we can do any possible test.

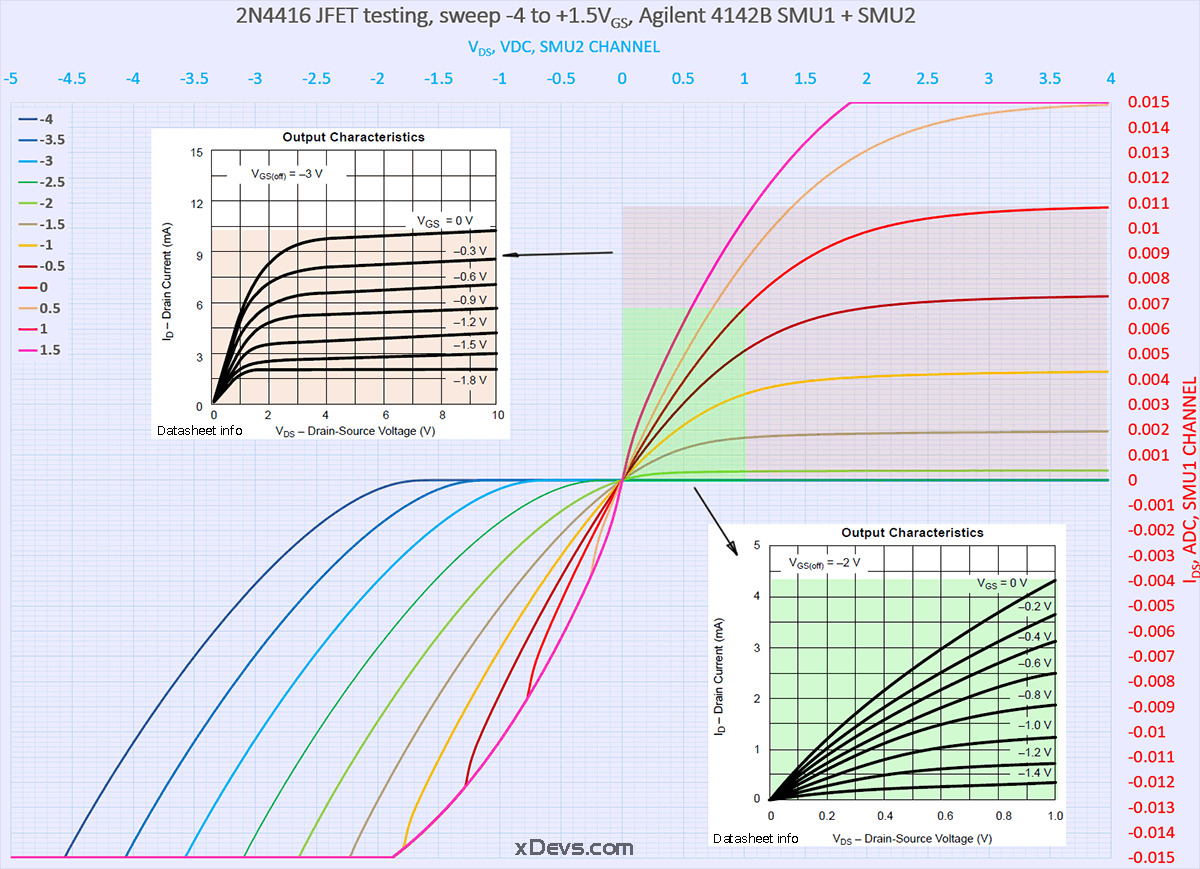

To get started, I connected random JFET from dead analog Keithley 2001 board (supposed to be 2N4416 N-channel JFET), and plot the I-V curve:

Excel-file on click.

Measurement result agree to datasheet curves well, so I can do next steps, if there are any suggestions. I have started this thread, because this also fits my current need to test unknown JFETs used in broken Keithley 2182A nanovolt-meter front end, so I'd like to use same setup to characterize them and see what their failure mode (input stage was overloaded with high-voltage surge).