Hi there Lattice MachXO3 developers,

I've got a couple of XO3-1300E boards here for a project that I ported from the MachXO3L-6900C breakout board.

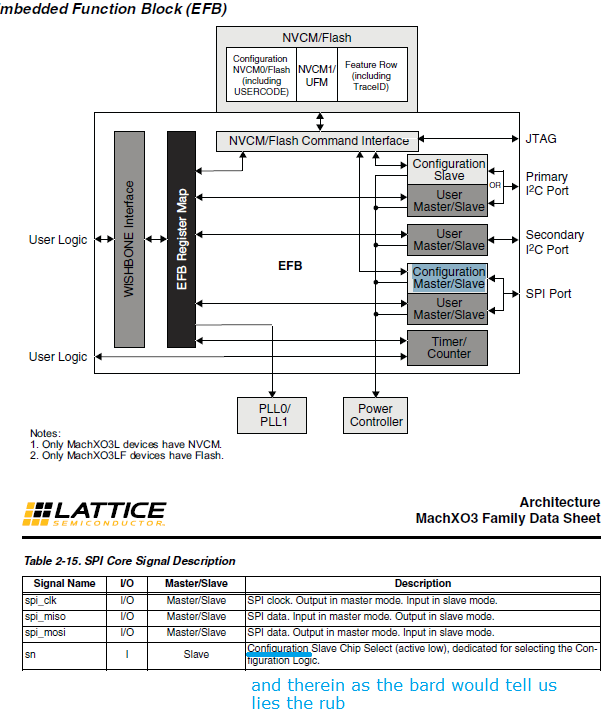

The design implements a SPI slave with SN used as chip select... and there's where the problem is: I need a way to deactivate the SPI configuration logic, free the SN sysConfig pin and make it available to the user mode Slave SPI als SCSN.

I may have missed the crucial point and here is why:

in the

MachXO3 Programming and Configuration Usage Guide they say that in user mode, the SN pin is used for SSPI. The EFB is hardened SPI afterall and SCLK, SPISO, SPISI also have dedicated I/Os for improved performance... so SN could also have a prefered pad? Not really.

It seems SN is the only one which can be connected via general routing routines and in turn cannot be mapped to a dedicated sysConfig pin of another slave SPI connected to the same pin.The problem arises when my preferences collide with sysCONFIG or other configuration options:

MachXO2 and MachXO3 devices offer multiple ports for configuration and programming, among these are JTAG (my prefered interface) and slave SPI.

It appears that at least when the slave SPI configuration port is activated outside user mode the SN pin is reserved for the configuration interface (think SPI multiplexed with two individual chip selects). So we gather SN is a sysConfig dediacted pin and....

You must prevent external logic from interfering with device programming. Make sure that recovered sysCONFIG

pins are not asserted when the MachXO3L/LF is in Feature Row HW Default Mode state. One example is driving

PROGRAMN with an active low signal after the MachXO3L/LF is in Feature Row HW Default Mode state. Failure

to reprogram the Feature Row with PROGRAMN disabled prevents the FPGA from configuring and entering user

mode.

Ok so slave SPI configuration is activated once the slave SPI is used (or even by default with the EFB being inactive in user mode) and thus SN cannot be used as CSN for user mode slave SPI?

Can I then deactivate the slave SPI configuration option and still use slave SPI in user mode with the SN pin as general purpose I/O (which then incidentally would be used to route CSN) ?

Right now I just get

ERROR - The state of the assigned pin [E1] conflicts with the config mode and cannot be assigned to the port (SPI_CSN).

indicating that the intended mapping collides with the exclusive character of SN for slave SPI configuration purposes (note there is a separate box for "configuration master/slave" attached to the same interface).

In principle all interfaces except JTAG could be disabled:

The MUX_CONFIGURATION_PORTS is used in the event that all configuration ports are disabled. Disabling all of

the available configuration ports turns the MachXO3L/LF into a “write one time” device.

MUX_CONFIGURATION_PORTS confirms the removal of all configuration ports. The control is only active when

all of the other configuration ports are set to the DISABLE state. MUX_CONFIGURATION_PORTS set to the

ENABLE state enables the JTAGENB input pin, permitting the JTAG port pins to be multiplexed. Setting

MUX_CONFIGURATION_PORTS to the DISABLE state causes the Diamond build tools to honor the removal of all

other configuration ports, allowing the MachXO3L/LF to become a “write one time” device.

That section confuses me. I've tried the option without success.

So the warning

61061045 WARNING - The SN pin is not available for use as a general purpose I/O pin when the SLAVE_SPI_PORT attribute is enabled. The SN pin should be tied high with an external pull-up if you are not using the Slave SPI port for configuration.

really means SN cannot be used as user mode chip select when the EFB Slave SPI is in use? In a less stupid moment I routed the JTAGENB input to a test pad.

Is there a way I can deactivate all configuration ports and re-activate JTAG on demand via JTAGENB, thereby making SN general purpose and available for user mode Slave SPI? Otherwise I'm looking at a new batch of PCBs :/

ps.

feature row settings are applied to the jedec file (way too late for it to cover the error arising in the first step (synthesis)). It is well hidden: synthesize your project, then with the .xcf programmer brought up go to Design>Utilities>Programming File Utility, in that editor load the .jed file, go to tools > feature row editor. Even there it seems that the only options are

- no Slave SPI

- Slave SPI in config mode, deactivated in user mode

- Slave SPI in config mode and preserved in user mode

No fourth option? But then what's the point of a MachXO3 if you can only have deactivated programming interfaces when you remove I2C and SPI along with them? I don't get it