## (at room temperature)

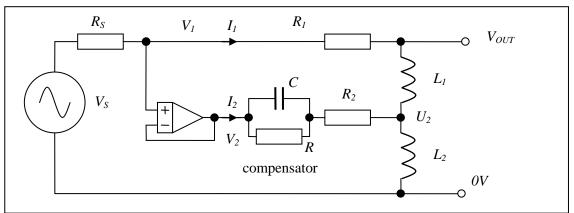

Faraday's toroidal transformer – the first on record (Picture courtesy of IET)

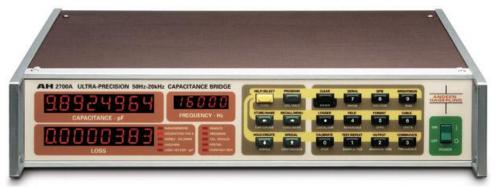

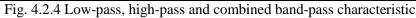

# A collection of monographs on inductive voltage dividers, ratio transformers and related circuits plus some nice maths

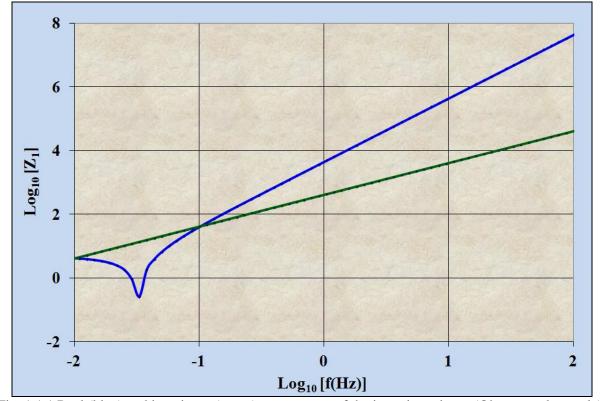

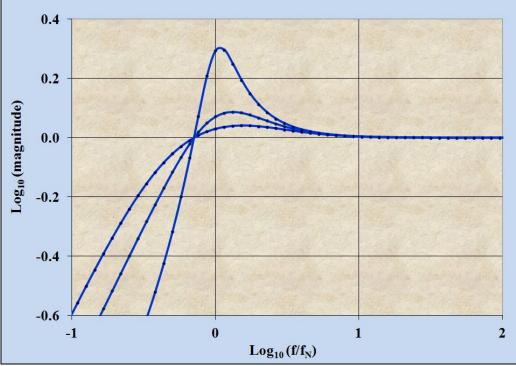

Version 1.0 (May 2020)

Christopher I. Daykin MA

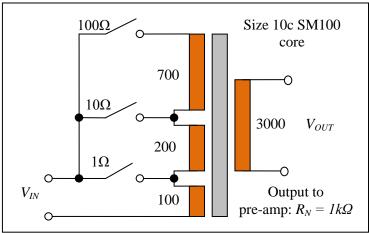

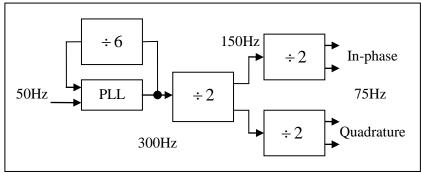

## Acknowledgements

For Di, with sincere thanks, in memory of John David Yewen FRAS (JDY): friend and former colleague. "Hairy" John taught me the art of engineering and deserves most of the credit for the ingenious designs herein.

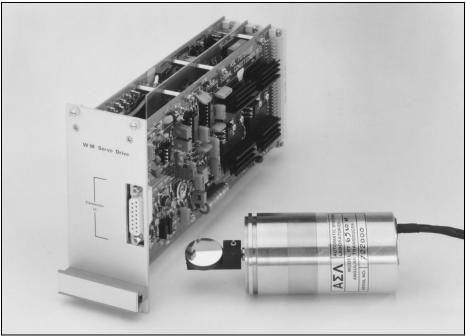

Thanks, also, to former ASL colleague: Peter Caleb Frederick Wolfendale FIEE [1].

Other contributions came from: -

- Don White [2] for extensive and valuable input on high accuracy resistors and guidance on publishing in general.

- Paul Bramley [3] for feedback on the monograph: The Isotech MicroK "Bridge".

- Professor Stephen Donnelly [4], for encouraging me to publish "for the benefit of mankind".

Thank you, also, Isothermal Technology Ltd and WIKA Alexander Wiegand SE & Co. KG for your permission to include certain images.

## Thanks guys!

More feedback would be appreciated.

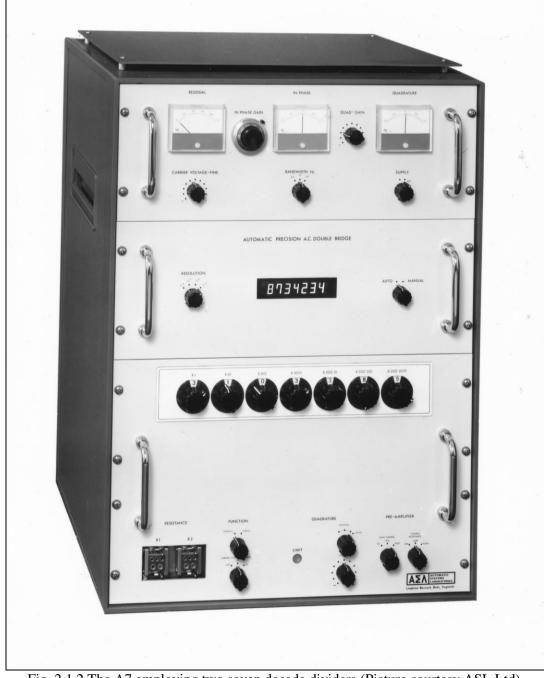

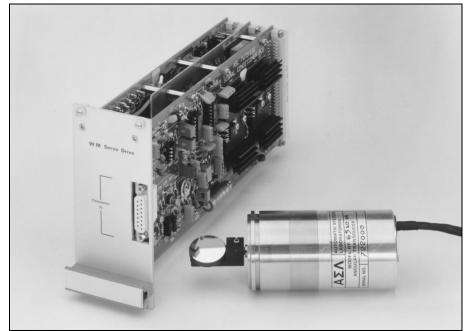

Inspirational founder and former Managing Director of Automatic Systems Laboratories Ltd.

Measurement Standards Laboratory of New Zealand and co-inventor (with Keith Jones) of the resistance bridge calibrator (RBC) - one of the most significant contributions to this field in recent years (Patent: PCT/NZ95/00022). See part 1, monograph 1, section 4.3 and 4.3.2

Metrosol Ltd and Project Manager of the MicroK Bridge design team.

4. University of Huddersfield and a genuine scholar.

## Preface

"High Accuracy" in the title refers to measurement uncertainty in the range of ten parts per million (10ppm) to ten parts per billion (10ppb). The subtitle "at Room Temperature" emphasises the fact that this level of accuracy is possible with readily available components, materials and tools. Whereas greater accuracy can be achieved at very low (cryogenic) temperature, such techniques are very expensive. A bridge based on the (superconducting) cryogenic current comparator [1], for example, exploits the Meissner effect and uses a superconducting quantum interference detector (SQUID) [2] to measure the ratio of resistors to better than 10ppb.

This collection is aimed, primarily, at students, teachers and researchers in the physical sciences. Some of the content could, for example, form the basis of a module at first degree (final year) level in electronic engineering. More advanced topics are suited to a Masters level course in metrology or instrumentation. Researchers could apply some of the techniques and practical tips to construct cutting edge instrumentation at minimal cost.

**Part 1** introduces the concepts of accurate lumped impedance: resistors and capacitors at low frequency. Threeterminal capacitors, for example, can be constructed for which the AC version of Ohm's law is accurate to within a few parts per billion. The theory is underpinned by Maxwell's field equations, surely one of the greatest scientific achievements of the nineteenth century, if not of all time.

The fundamental mechanism that gives rise to the concept of resistance, on the other hand, is much more complicated. Fortunately we have decades of technological development and empirical evidence, at low frequency, to underpin our faith in Ohm's law, at least to the level of 10ppb, for many types of materials and components.

**Part 2** also deals with (mainly) passive components - in circuits to form high accuracy filters. These are not only useful but also instructive - the models developed and "nice" matrix maths is applied in later monographs (for the analysis of two and three-stage inductive voltage dividers and ratio transformers).

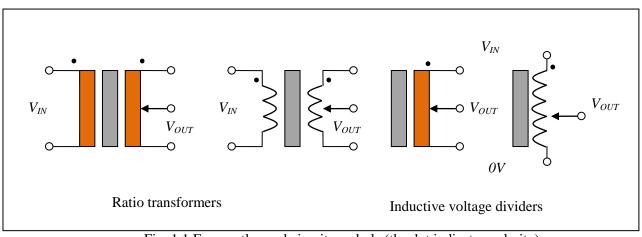

**Parts 3 and 4** are the core of the collection: inductive voltage dividers (IVDs), ratio transformers (RTs) and related accurate circuits, especially the "inside-out" high accuracy voltage follower (HAVF). A review of basic principles is provided for students but the advanced specialist may also find some useful ideas which have remained unpublished for over 35 years.

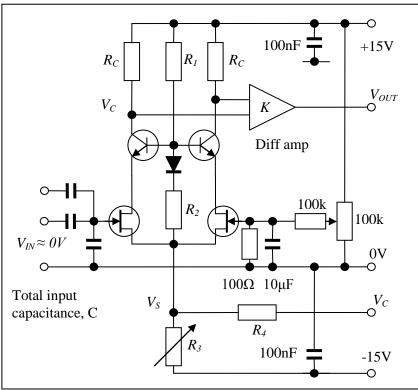

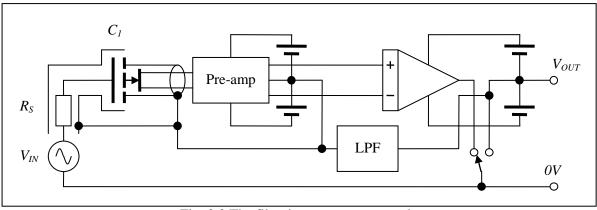

**Parts 5 and 6** are concerned with other circuits which, despite not being inherently accurate, are indispensible. A well matched low noise pre-amplifier and filtering for potentially large amounts of interference are, for example, essential ingredients of a good null detector. Included in the miscellany are a couple of unusual circuits which may not be found in any text book or application note: A simulated large capacitor and a simulated negative capacitor are further examples of JDY's ingenuity.

Most of the content should be uncontroversial but there are a few notable exceptions. This author "begs to differ" with the generally accepted definition of a four-terminal-pair lumped impedance [3]. An alternative is proposed.

Also, the term "Bridge" as in [4] is debatable; The MicroK "Bridge" is based on a high accuracy analogue to digital converter (ADC) with 10ppb linearity. An attempt is made to explain how this incredible performance is achieved.

Similarly, the HP3458A digital multi-meter (DMM) is based on a proprietary "multi-slope" ADC technique. Much of its workings remain "trade secret". The theory here is based on scraps of published information [5].

Some of the content is speculative – novel but untested designs. The interested reader is encouraged to contact the author (email: <u>hiaccelectronics@gmail.com</u>).

1. Seppä, H. and Satrapinski, A.: "AC Resistance Bridge Based on the Cryogenic Current Comparator". IEEE Trans. on Inst. & Meas., Vol. 46, No 2, April 1997.

2. A SQUID can detect extremely low levels of magnetic flux density (typically  $\approx 3aT/\sqrt{Hz}$ ).

3. Part 1, Monograph 1, section 2.1.

- 4. Part 4, Monograph 4: The Isotech MicroK "Bridge".

- 5. Part 4. Monograph 5: The 3458A general purpose digital multi-meter.

## CONTENTS

## Part 1: High accuracy passive components

## Monograph 1: High accuracy resistors

- 1. Introduction

- 2. Three-terminal resistors (two terminals plus screen)

- 2.1 Converting to a four-terminal pair resistor

- 3. Two-terminal-pair resistors

- 3.1 Analysis of parallel capacitance with quadrature balance

- 3.1.1 Example calculation

- 3.2 Analysis of parallel capacitance without quadrature balance

- 3.2.1 Example calculation

- 3.3 Quadrature due to series inductance

- 3.4 Two-terminal-pair zero-Ohm junctions

- 4. Two-terminal-pair resistor networks

- 4.1 Introduction

- 4.2 Balancing (potential sharing) resistors

- 4.3 Resistance bridge calibrators

- 4.3.1 The Hamon "build-up" network

- 4.3.2 The White/Jones resistance bridge calibrator

- 5. Four-terminal-pair resistors

- 5.1 Example calculations

- 5.1.1 Cable phase and magnitude errors

- 5.1.2 Zero-Ohm junction errors

- 5.1.3 HGB error voltage

- 5.1.4 Resistance in cable 4

- 5.2 4TP resistors with calculable quadrature

- 6. Johnson Noise

## Monograph 2: High accuracy single capacitors

- 1. Introduction

- 2. Transfer standard air capacitors

- 3. Basic principles

- 4. The Thompson Lampard calculable capacitor

- 5. Industry standards

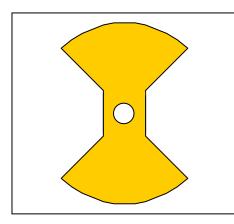

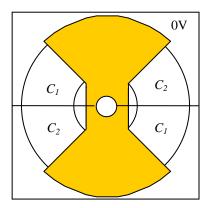

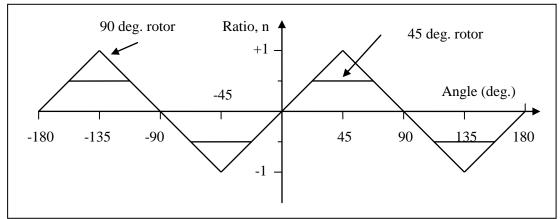

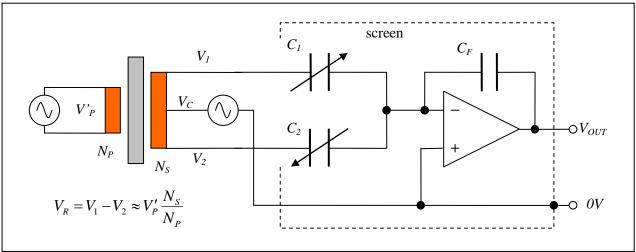

## Monograph 3: Rotary capacitive displacement transducers

- 1. Introduction

- 1.1 The two main types

- 1.2 The basic principle of operation

- 2. Ratiometric operation

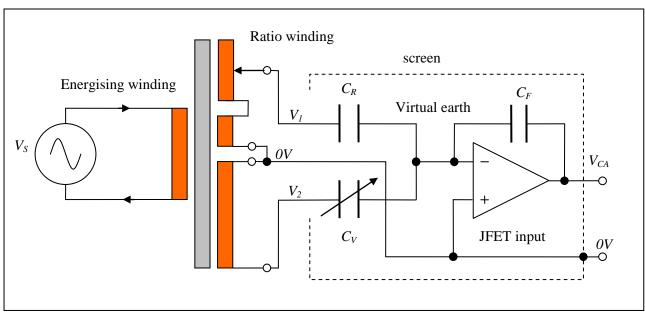

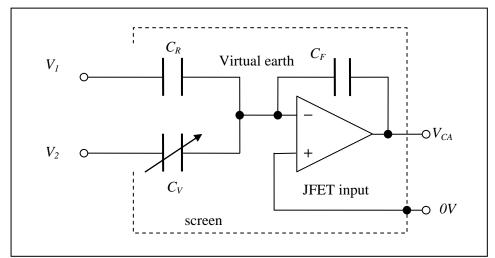

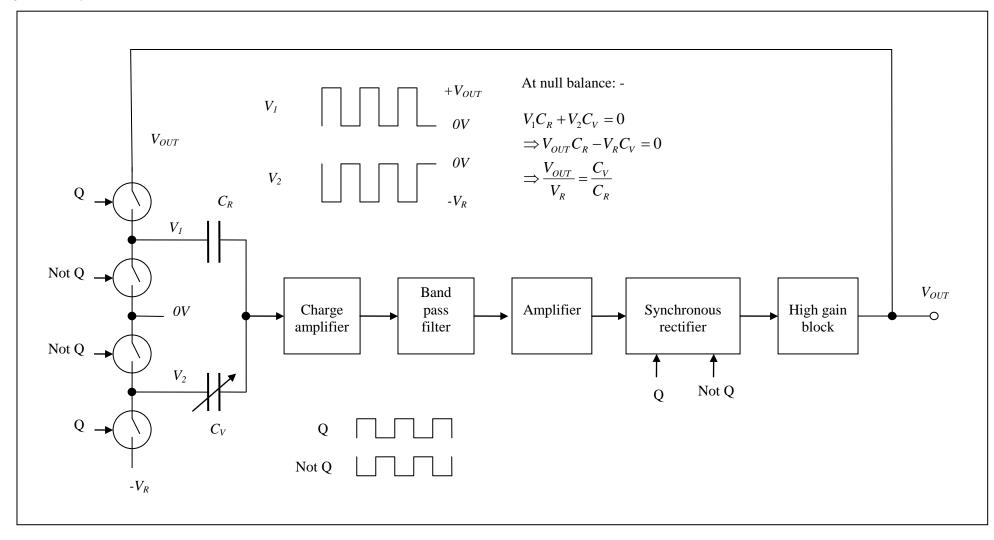

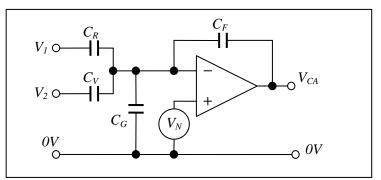

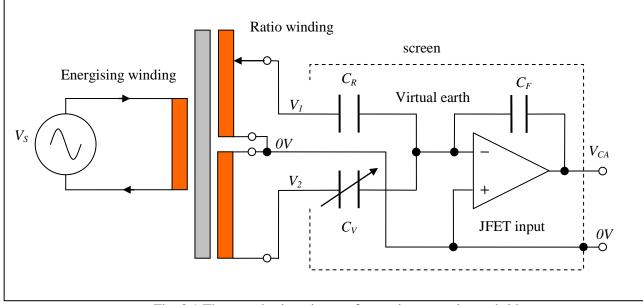

- 3. The charge amplifier

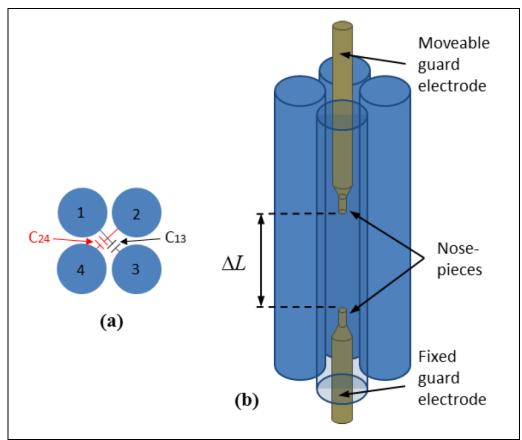

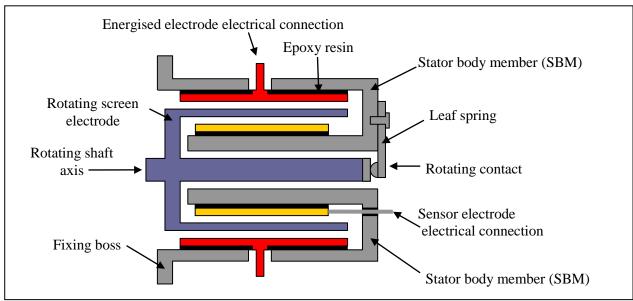

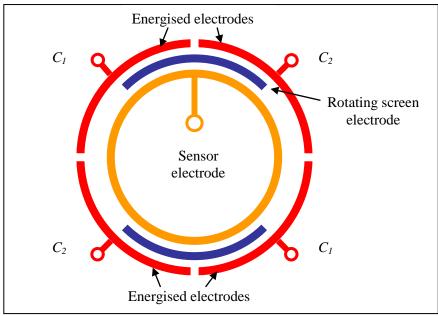

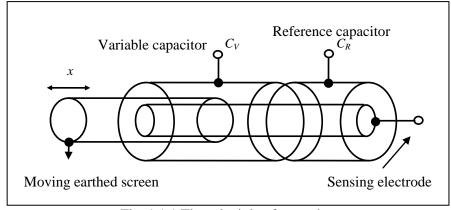

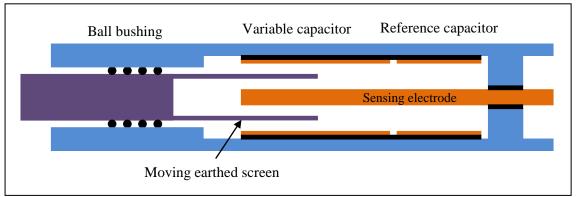

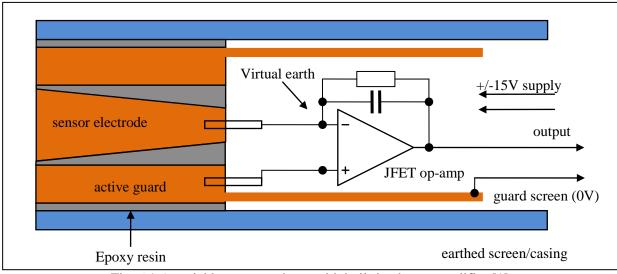

- 4. The cylindrical type transducer

- 5. Plate type transducers

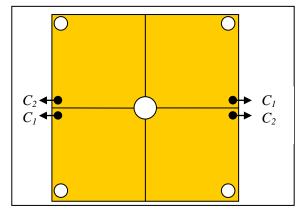

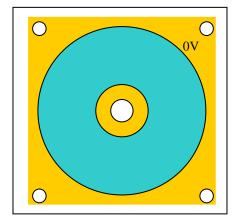

- 5.1 A low cost limited angle example

- 5.2 A multi-segmented design

- 6. Low cost signal conditioning

- 7. Noise analysis

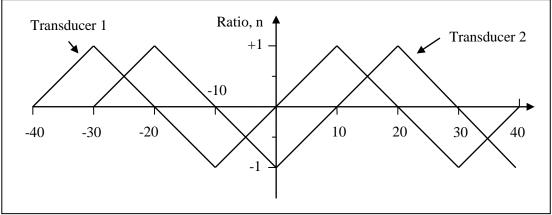

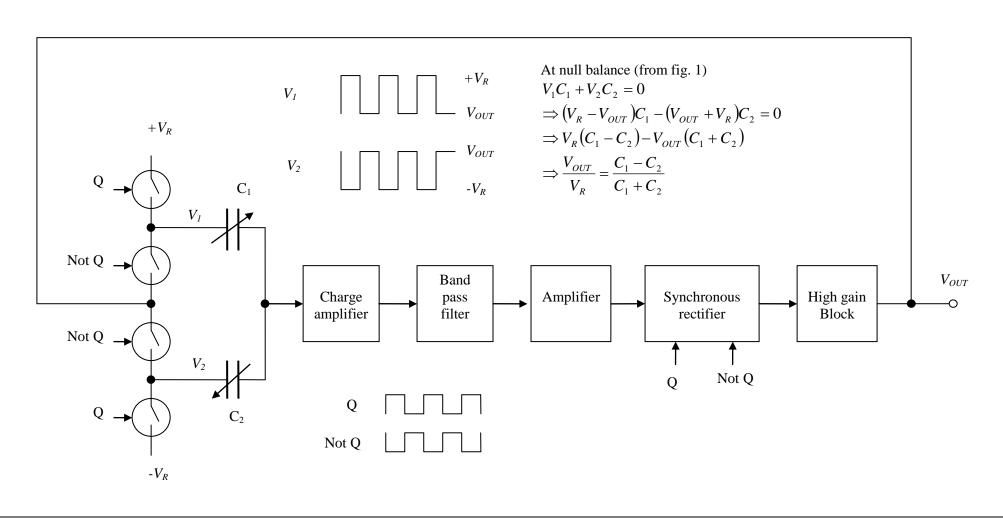

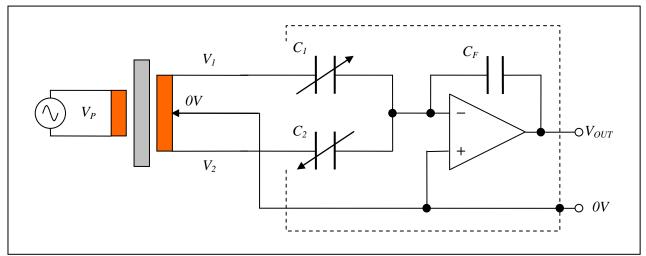

#### Monograph 4: Linear Capacitive Displacement Transducers

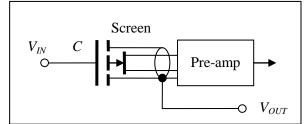

- 1. Introduction

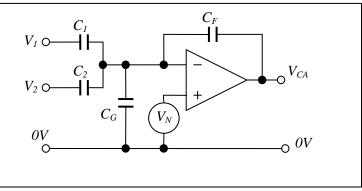

- 1.1 The principle of operation

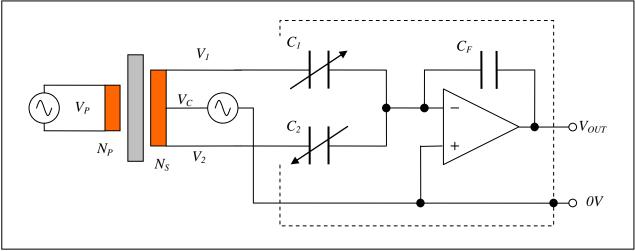

- 2. Ratiometric operation

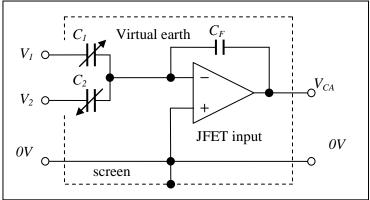

- 3. The charge amplifier

- 4. A low cost signal conditioner

- 5. Noise analysis

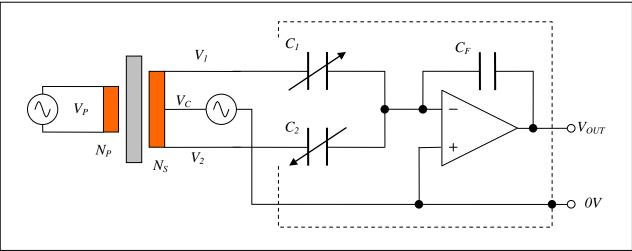

## Monograph 5: Variable gap capacitive displacement transducers

- 1. Introduction

- 1.1 Profile measurement

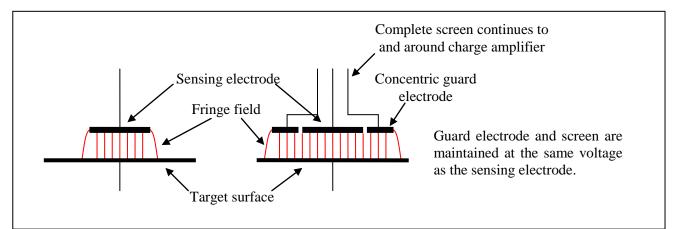

- 2. The guard electrode and charge amplifier

- 2.1 The charge amplifier

- 3. The Ratio transformer/capacitance bridge 3.2 Earthing the target surface

- 4. Noise analysis

## Monograph 6: Low phase error capacitors and inductors

- 1. Introduction

- 2. Polypropylene capacitors

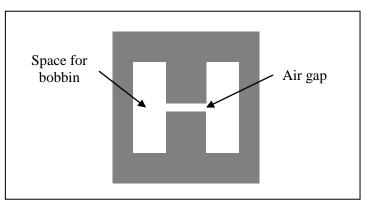

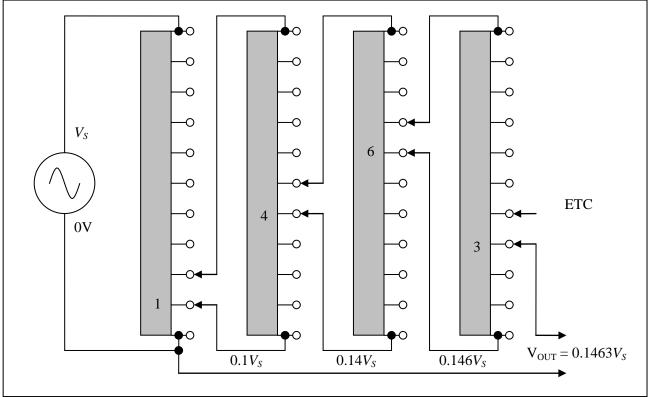

- 3. Low phase error ferrite transformers

- 3.1 Example calculation

- 3.2 A practical differentiator circuit

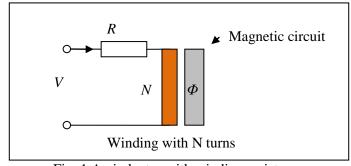

- Appendix: Magnetic circuit theory (basics)

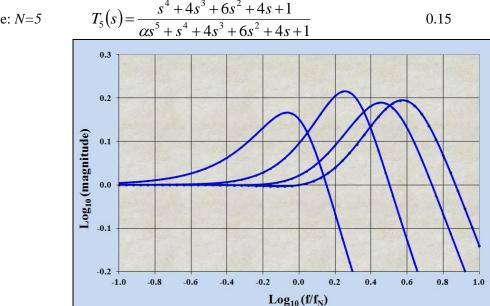

## Part 2: High Accuracy Filters

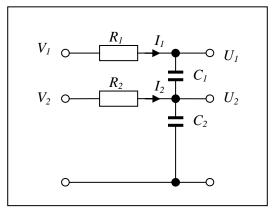

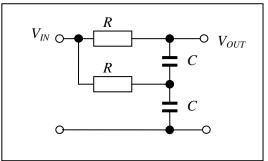

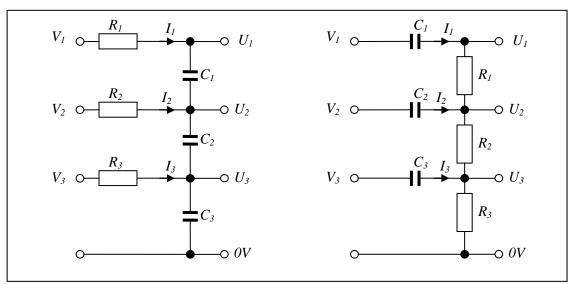

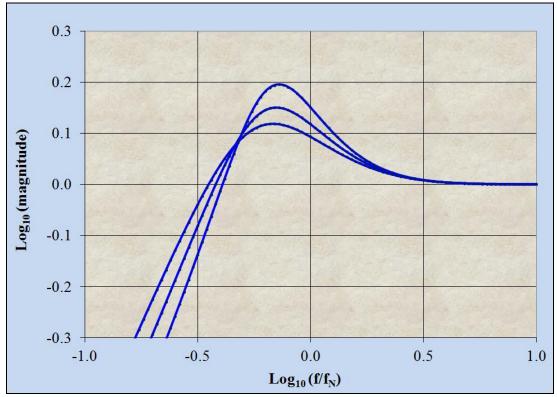

## Monograph 1: Two-stage filters

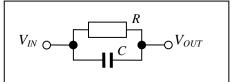

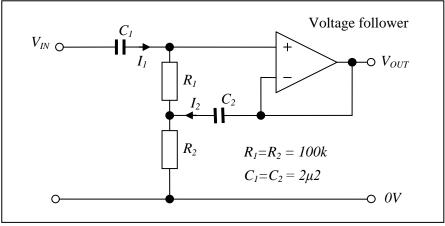

- 1. Introduction

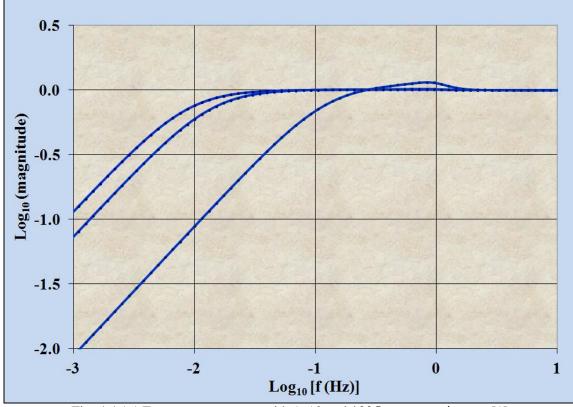

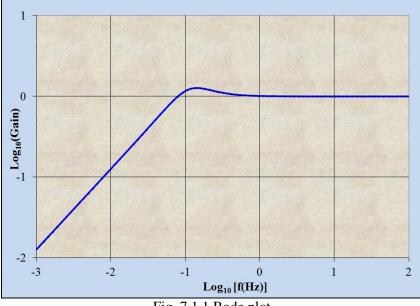

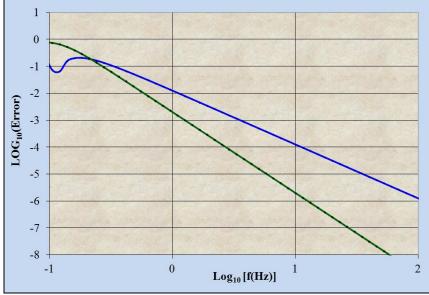

- 2. Two-stage low pass filters

- 2.1 Network analysis

- 2.2 A basic two-stage low pass filter

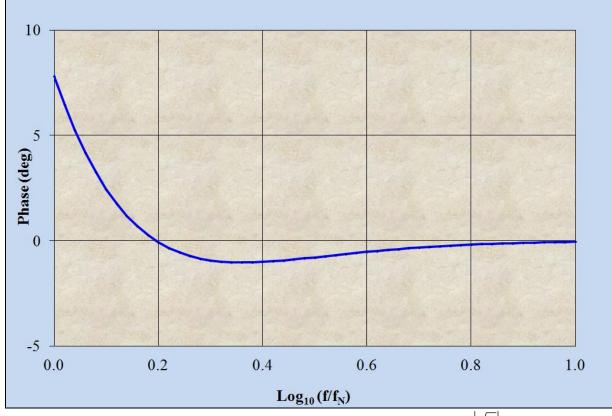

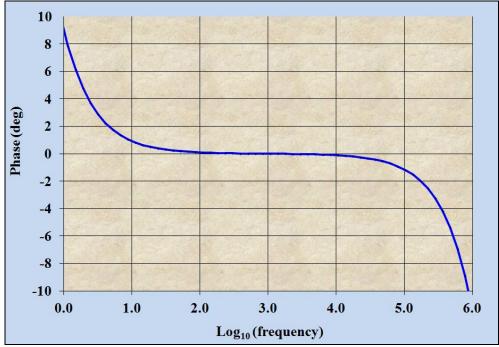

- 2.2.1 Phase shift at low frequency

- 2.3 Different values of resistors and capacitors

- 2.3.1 Example calculation: The minimum (a = 2)

- 2.3.2 Example calculation 2: For a relatively high value (a = 4)

- 2.3.3 Widely different values for resistors and capacitors

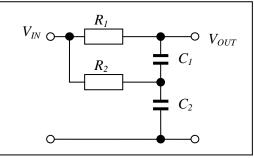

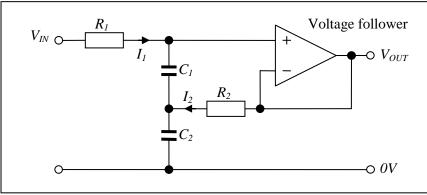

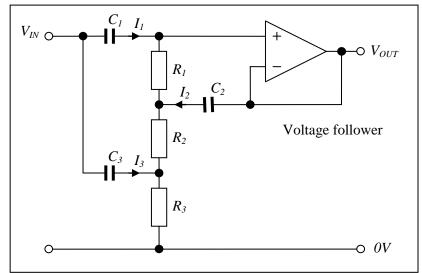

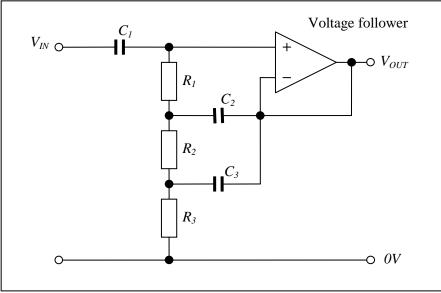

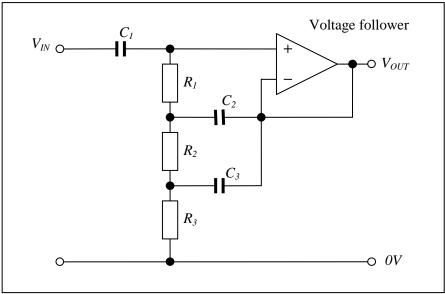

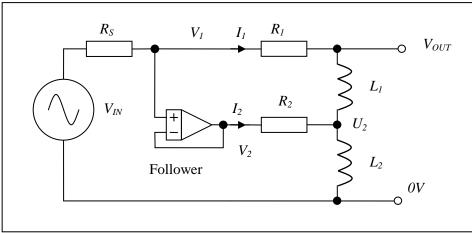

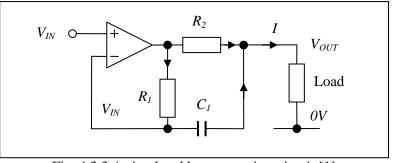

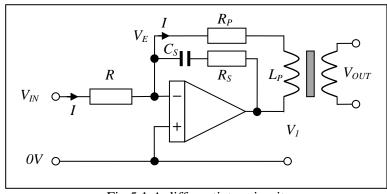

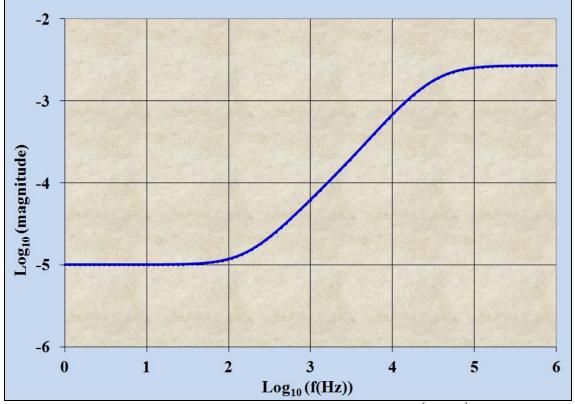

- 3. Actively driven low pass filters

- 3.1 Network analysis

- 3.2 Equal resistor and capacitor values

- 3.3 Different values of resistors and capacitors

- 3.3.1 Example calculation

- 3.4 Widely different values of resistors and capacitors.

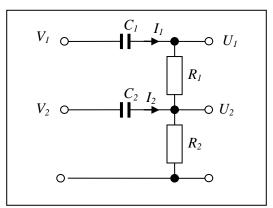

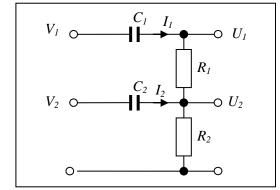

- 4. Two-stage high pass filters

- 4.1 Network analysis

- 4.2 A basic two-stage low pass filter

- 4.2.1 Phase shift at high frequency  $(\omega >> \omega_N)$

- 4.2.2 Equal resistor and capacitor values

- 4.3 Equal resistor and capacitor values

- 4.4 Different values of resistors and capacitors

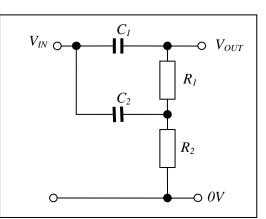

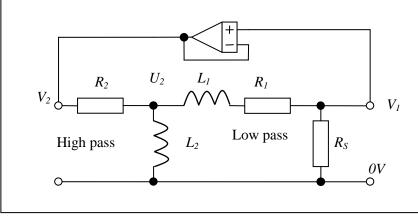

- 5. Actively driven two-stage high pass filters

- 5.1 Circuit analysis

- 5.1.1 Phase error at high frequency

- 5.2 Equal resistor and capacitor values

- 5.3 Different values of resistors and capacitors

- 5.3.1 Example calculation

- 5.4 Widely different values of resistors and capacitors

- 5.5 Input impedance

- 5.5.1 Example calculation

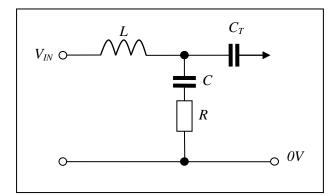

- 6. An LCR low-pass filter with two-stage response

- 6.1 Introduction

- 6.2 Circuit analysis

- 6.3 Output impedance

## Monograph 2: Three-stage filters

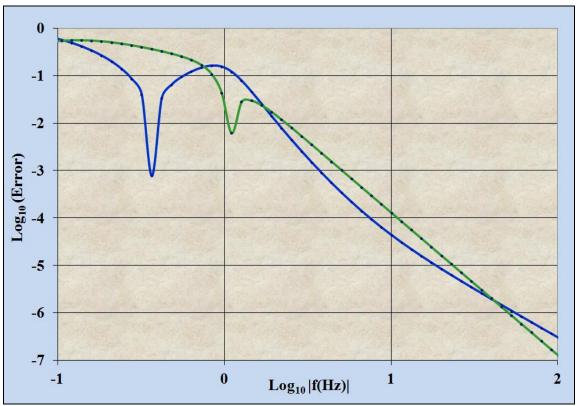

## 1. Introduction

- 1.1 Network analysis

- 1.2 Cramer's Rule

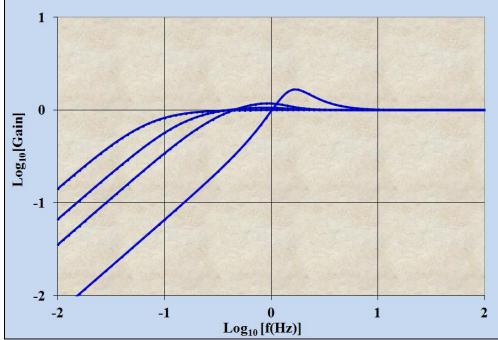

- 2. Actively driven three-stage bootstrapped high pass filter (type 1)

- 2.1 Circuit analysis

- 2.2 A basic type 1 filter

- 2.3 Different values of resistors and capacitors

- 2.4 Errors at high frequency  $(\omega >> \omega_N)$

- 2.4.1 An interesting result

- 2.5 Calculating component values

- 2.5.1 Example calculation

- 3. Actively driven three-stage high pass filter (type 2)

- 3.1 Circuit analysis

- 3.2 A basic type 2 filter

- 3.3 Different values of resistors and capacitors

- 3.4 Calculating component values

- 3.5 Input impedance

- 3.5.1 Example calculation

- Appendix 1: Cramer's method for matrix inversion (Three-stage high-pass network)

- Appendix 2: Calculating the determinant (Three-stage high-pass network)

- Appendix 3: Calculating transfer functions

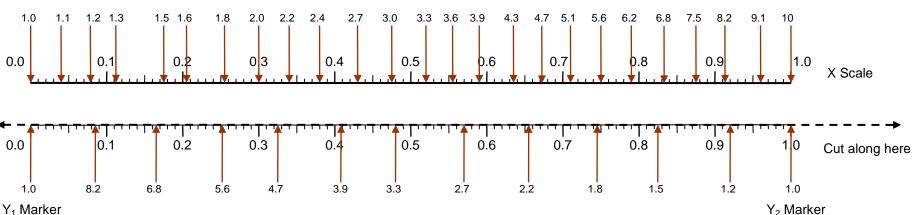

- Appendix 4: Slide rule calculator for RC combinations

## Monograph 3: An ultra-high input impedance high pass filter

- 1. Introduction

- 2. Outline design proposal

- 3. A low cost version

## Part 3: Inductive Voltage Dividers and Ratio Transformers

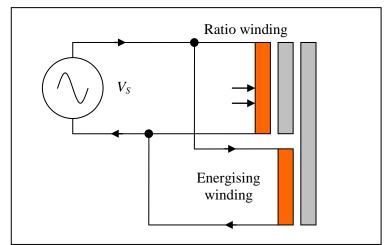

## Monograph 1: IVDs and RTs – the basics

- 1. Introduction

- 1.1 Applications

- 1.2 Leakage flux

- 1.3 Winding schemes

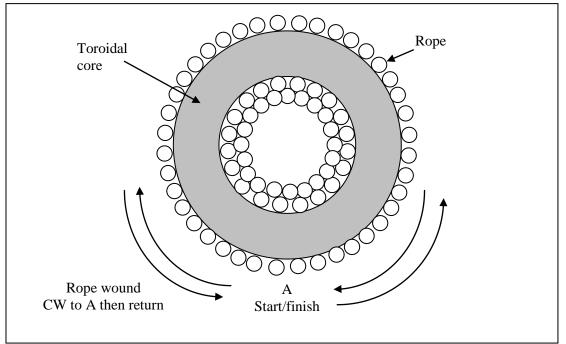

- 1.3.1 The "no-net-loop" (NNL) method

- 1.3.2 The "balanced no-net-loop" (BNNL) method

- 1.3.3 The NNL and BNNL methods applied to low number of turns of energising windings.

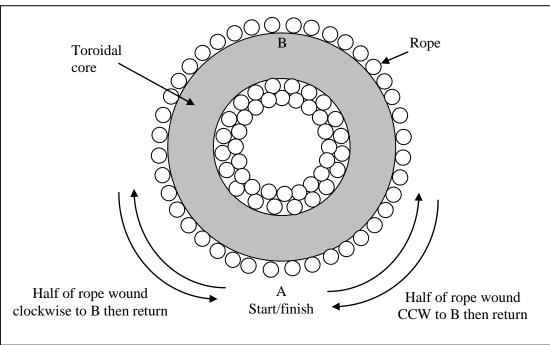

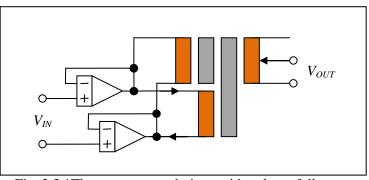

- 2. The basic inductive voltage divider

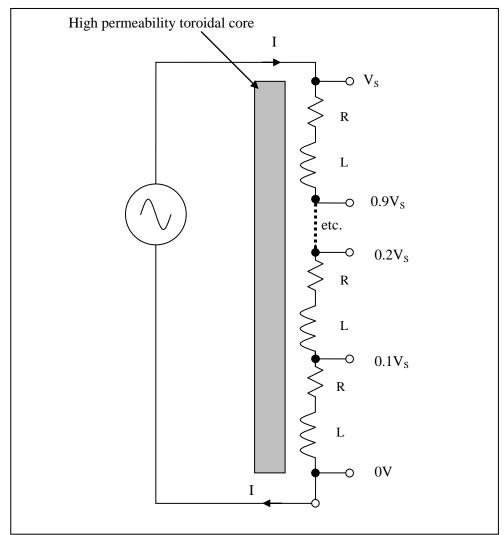

- 2.1 Multi-decade IVDs

- 2.2 The two-stage IVDs

- 2.3 The two-stage IVD with high accuracy voltage followers

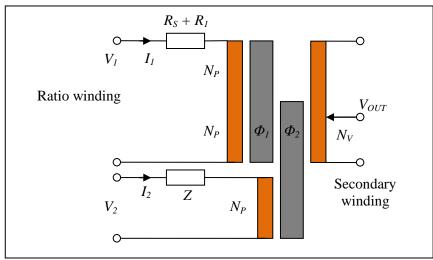

- 3. The basic ratio transformer

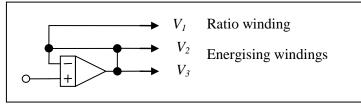

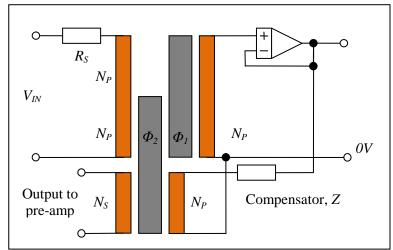

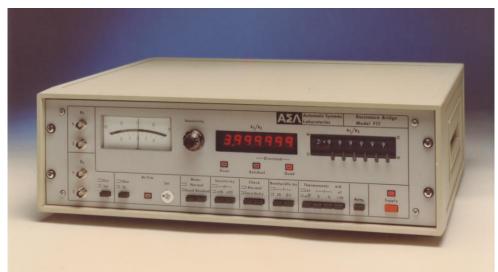

- 4. The three-stage ratio transformer (e.g. ASL model F17)

- 5. An advanced three-stage ratio transformer (e.g. ASL model F18)

- 6. A three-stage current transformer (NPL's "Knight" bridge)

- 7. Kusters' comparator (e.g. Guildline model 6622T)

- 8. The double balanced potentiometer (e.g. The ASL "Cryo-bridge" [1])

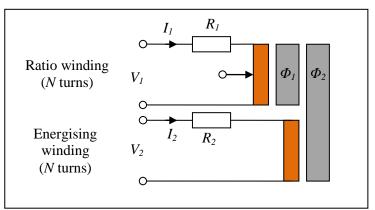

## Monograph 2: Single-stage inductors and transformers

- 1. Introduction

- 2. Calculating impedance from basic parameters

- 3. High levels of flux density and core saturation

- 3.1 Example calculation

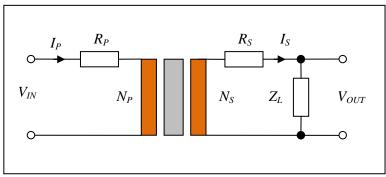

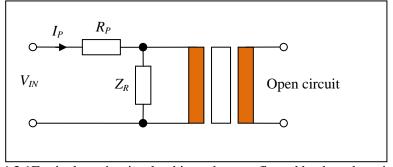

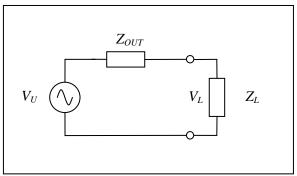

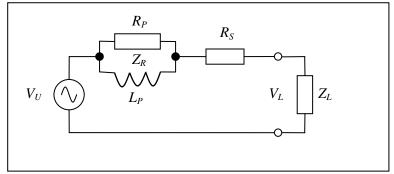

- 4. Basic transformer theory

- 4.1 Current transformers

- 4.2 Voltage transformers

- 4.2.1 Example calculation

- 4.3 Input impedance

- 4.4 Output impedance

- 4.5 Capacitive load impedance

- 4.5.1 Example calculation

- 4.6 A single-stage resistance bridge

- 5. Inductive voltage dividers (auto-transformers)

- 6. Equalising windings

- 6.1 Example calculation

- Appendix 1: Toroidal core data courtesy Telcon

- Appendix 2: Copper wire data.

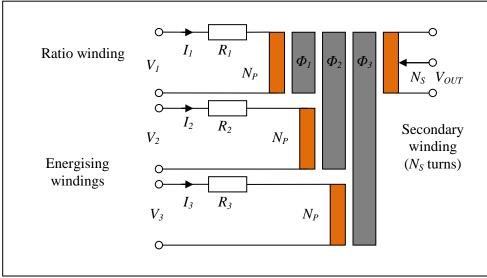

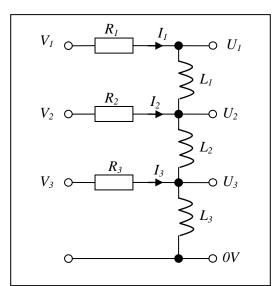

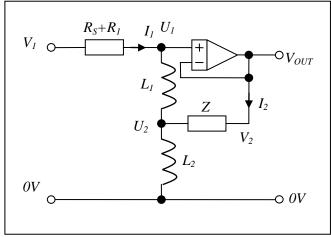

## Monograph 3: Two-stage IVDs and RTs

- 1. Two-stage IVDs

- 1.1 Example calculation

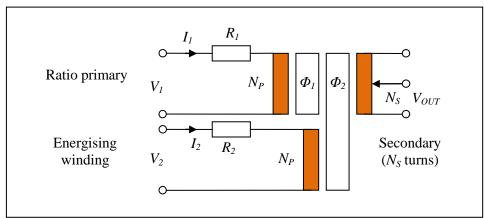

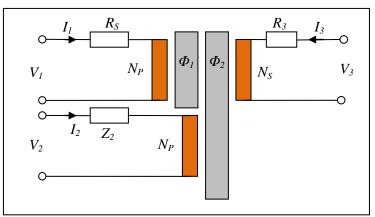

- 2. Two-stage transformers

- 2.1 Example calculation

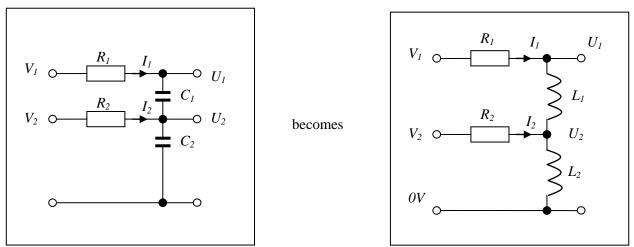

- 3. The matrix method and the equivalent circuit

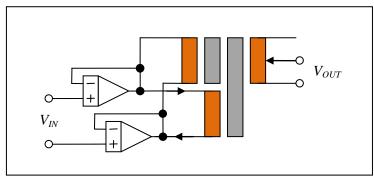

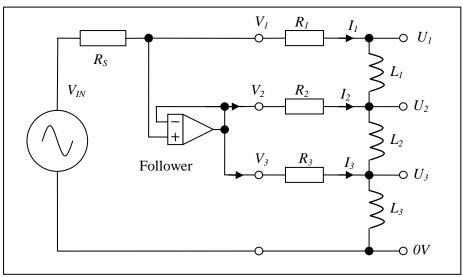

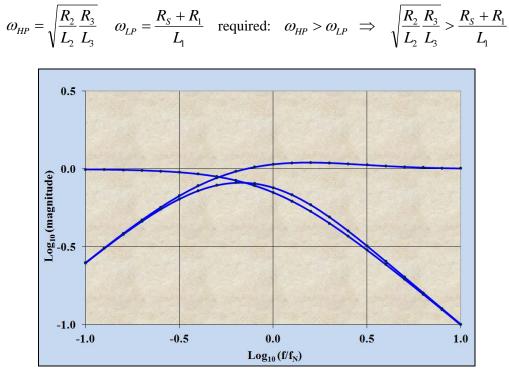

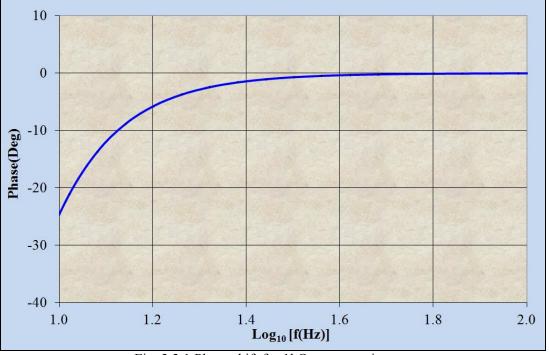

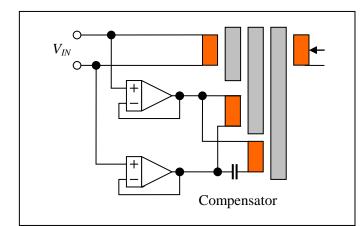

- 4. Two-stage active drive and stability

- 4.1 Active drive for both primary windings

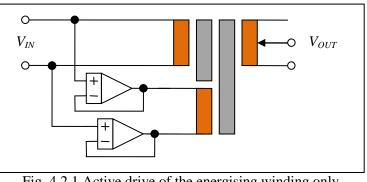

- 4.2 Active drive for the energising winding only

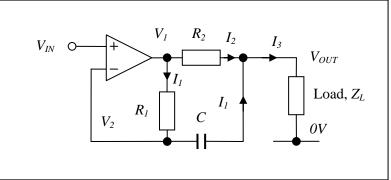

- 4.2.1 Network analysis

- 4.2.2 Stability analysis (approximate)

- 4.2.3 Example calculation

- 4.2.4 Errors in the energising follower

- 4.2.5 Follower noise

- 4.2.6 The effect on input impedance

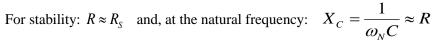

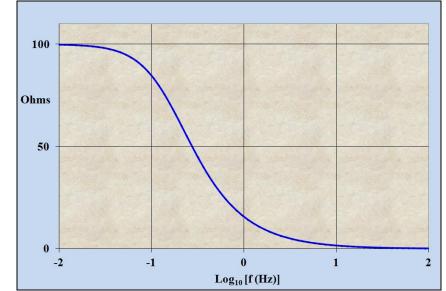

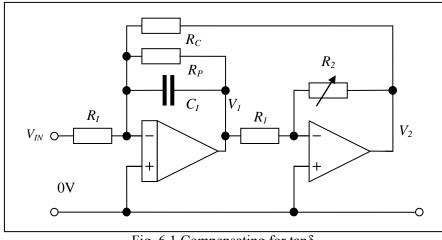

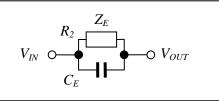

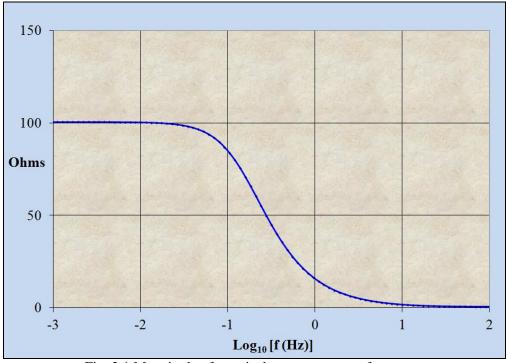

- 4.3 Active drive with compensator (resistor/parallel capacitor)

- 4.3.1 Error analysis with compensator

- 4.3.2 Example calculation

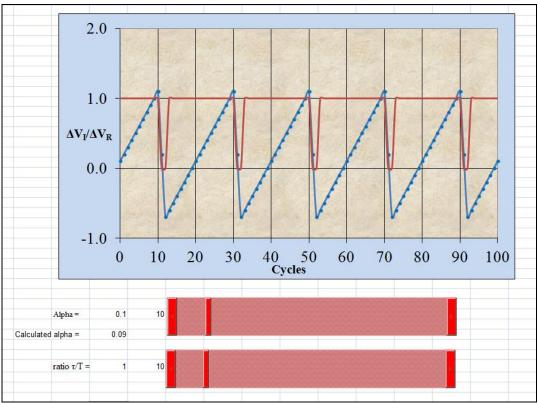

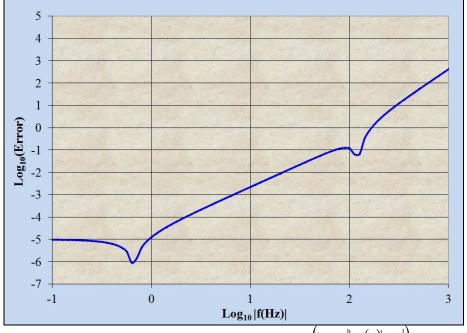

- 4.3.3 Spreadsheet simulation

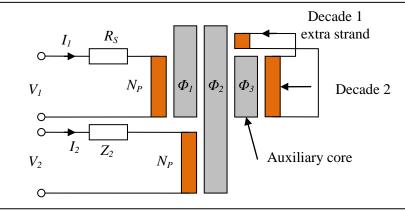

- 4.4 Extra turns around the top core

- 4.4.1 Example calculation

- 5. Loading effects

- 5.1 Loading the energising core

- 5.1.1 The effect on energising accuracy of loading the energising secondary

- 5.1.2 Loading the energising core and its effect on ratio accuracy

- 5.2 Loading the ratio secondary

- 6. Equalising windings

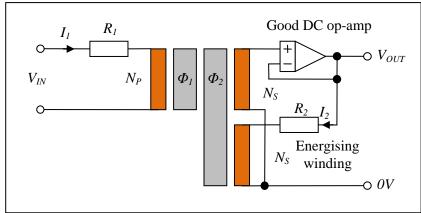

- 7. Energising from the secondary

- 7.1 Example calculation

- Appendix 1: Toroidal core data courtesy Telcon and copper wire data.

- Appendix 2: detailed equation bashing (see section 4.3): -

- Appendix 3: the inverse of a  $3 \times 3$  matrix

## Monograph 4: Three-stage RTs

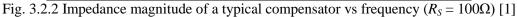

## 1. Introduction

- 1.1 The effects of follower errors, noise, loading and equalisation of windings

- 2. Active drive for all three primary windings

- 2.1 Input currents and impedances

- 2.2 The transfer function

- 2.3 Example calculation

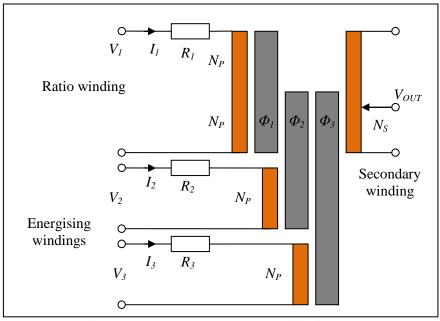

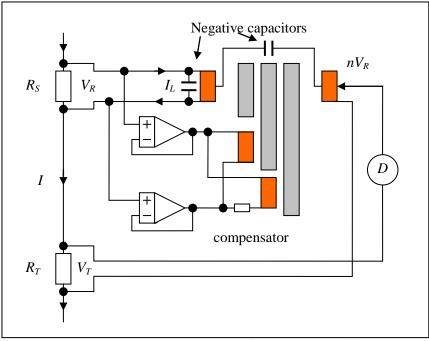

- 3. Active drive for energising windings only

- 3.1 The importance of source resistance

- 3.1.1 Example calculation

- 3.2 Active drive with compensator

- 3.2.1 Error analysis

- $3.3\ \mathrm{Extra}\ \mathrm{turns}\ \mathrm{around}\ \mathrm{the}\ \mathrm{top}\ \mathrm{core}$

- 3.3.1 Example calculation

- 4. Energising from the secondary

- Appendix 1: Equation bashing

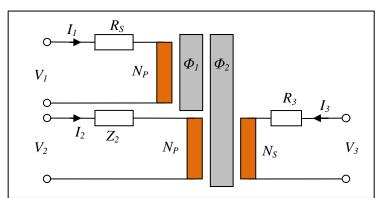

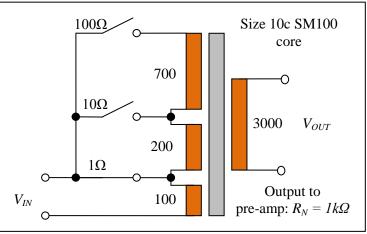

## Monograph 5: Noise matching transformers

- 1. Introduction

- 2. A single-stage transformer

- 3. A possible two-stage transformer

- 3.1 Outline design

- 3.2 Circuit analysis

- 3.3 Example calculation

Appendix: Toroidal core data courtesy Telcon and copper wire data

## Monograph 6: An F17 type ratio transformer bridge

- 1. Introduction

- 1.1 The basic principle of operation

- 1.2 Active guard circuit

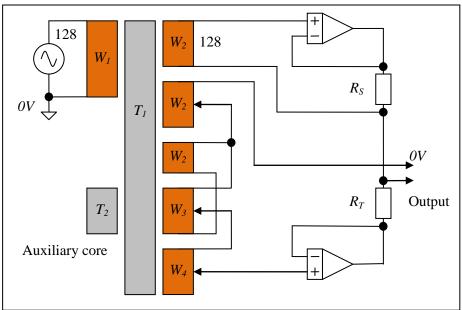

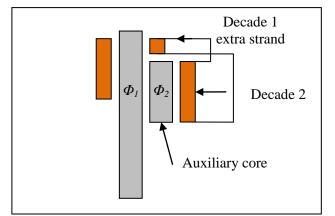

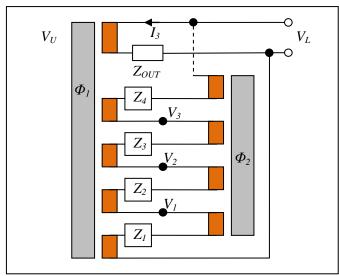

- 2. The main ratio transformer [2]

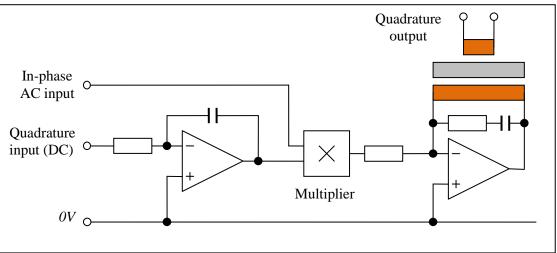

- 3. Quadrature servo and null detector

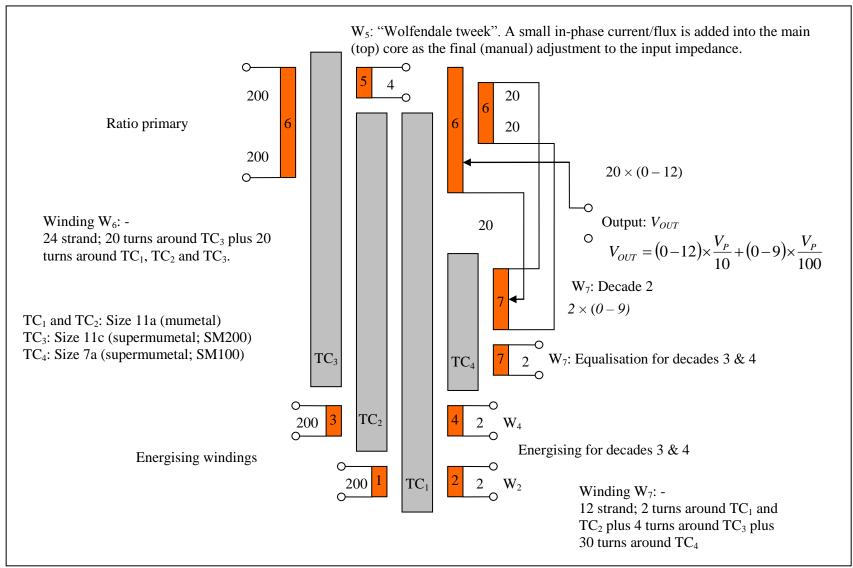

## Monograph 7: An F18 type ratio transformer bridge

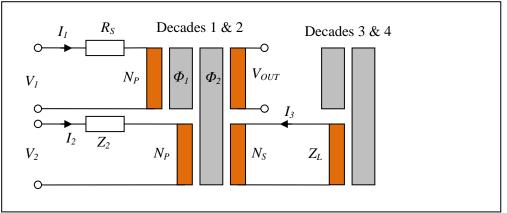

- 1. Introduction

- 2. The basic principle of operation

- 3. Active guard circuit

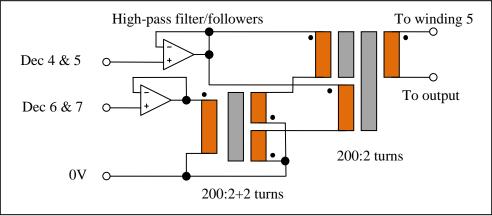

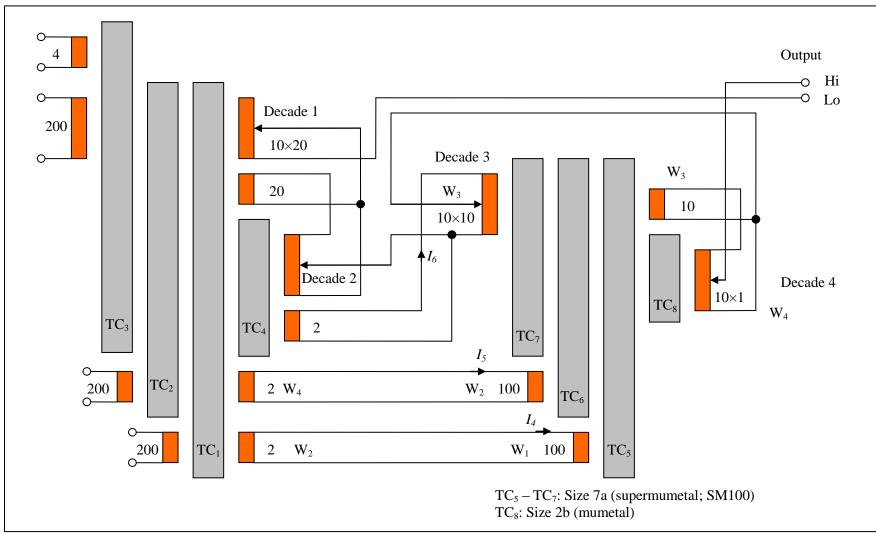

- 4. The divider

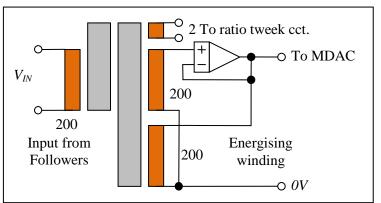

- 4.1 The ratio transformer 1 (decades 1 and 2)

- 4.2 The ratio transformer 2 (decades 3 and 4)

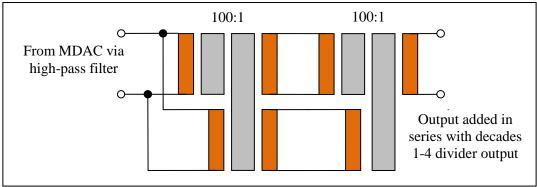

- 4.3 The resistive multiplying R-2R DAC

- 5. Quadrature servo and null detector

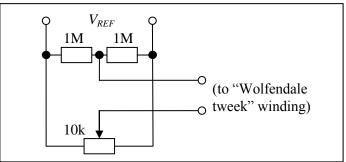

- 6. Manual "tweeks"

- 6.1 The ratio tweek

- 6.2 The input impedance tweek

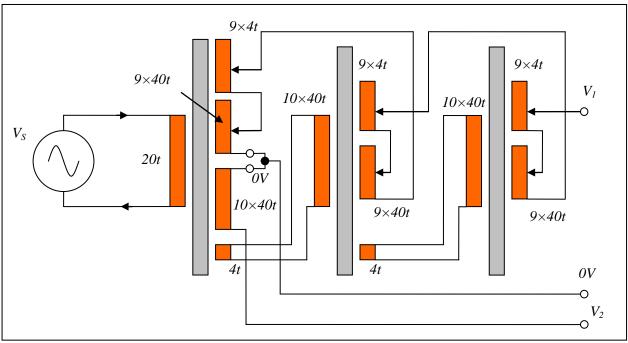

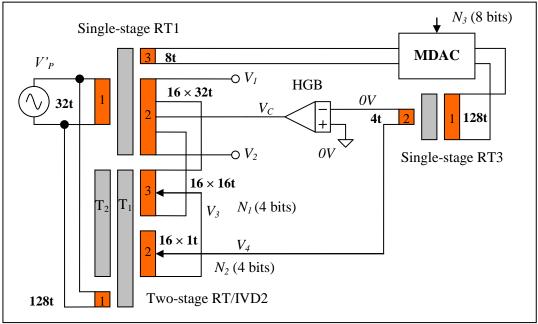

## Monograph 8: A 16 bit binary differential capacitance bridge

- 1. Introduction

- 2. Design details [1]

- 2.1 The single stage ratio transformer (RT1)

- 2.2 The two-stage inductive voltage divider (RT/IVD2)

- 2.3 The single stage ratio transformer (RT3)

- 2.4 The MDAC

Work in progress: -Monograph: 9\_Coaxial AC bridges Monograph: 10\_A quadrature bridge

## Part 4: High accuracy active circuits

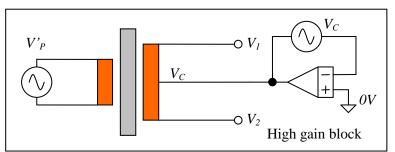

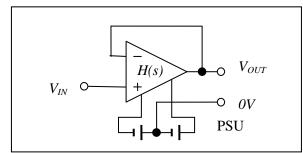

## Monograph 1: High gain blocks

- 1. Introduction

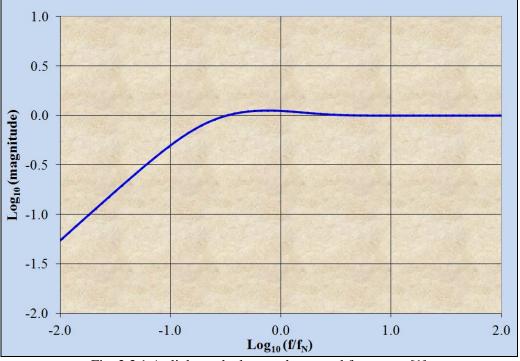

- 2. Feedback, stability and accuracy (general theory)

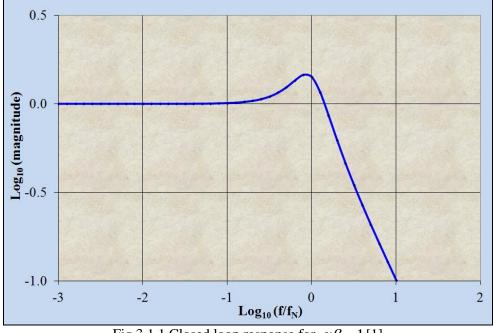

- 2.1 The closed loop transfer function

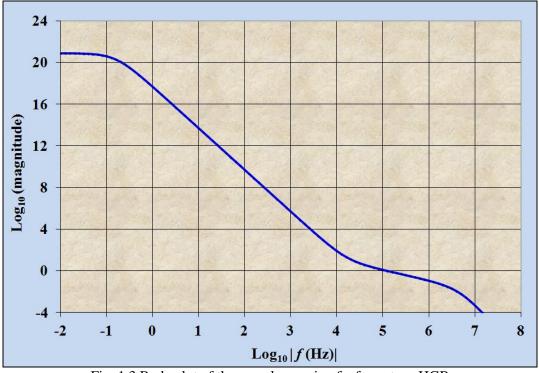

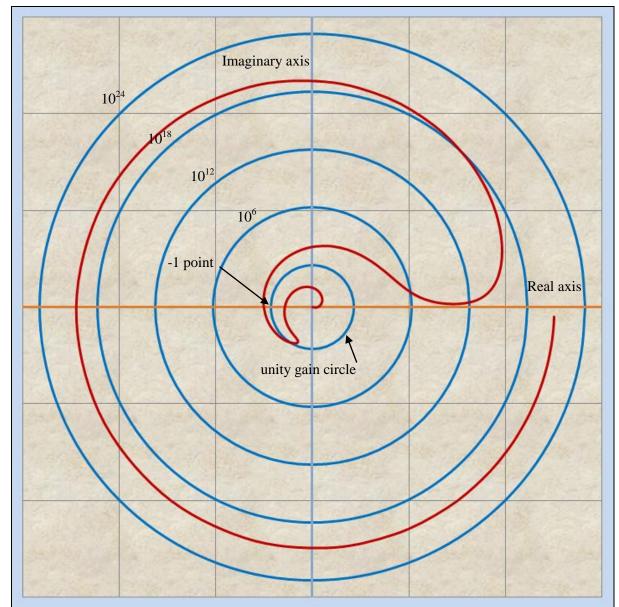

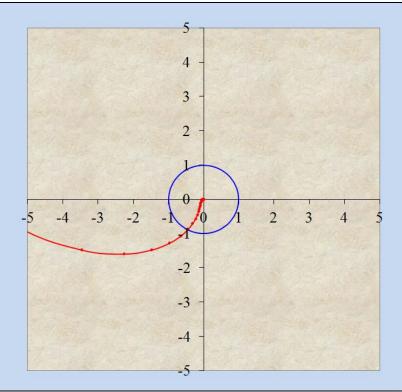

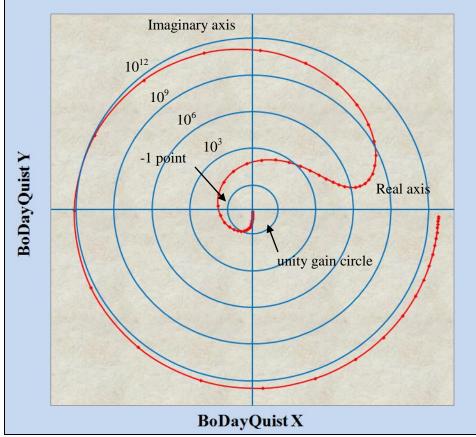

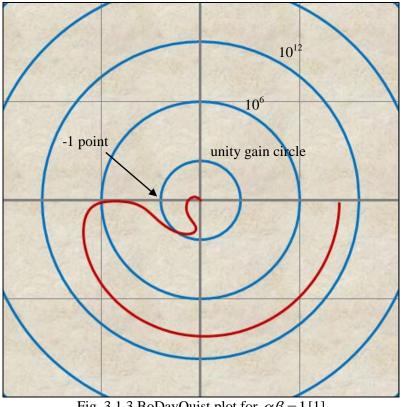

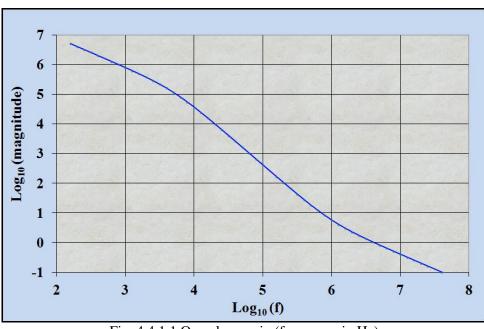

- 2.2 The Bardayquist stability criterion.

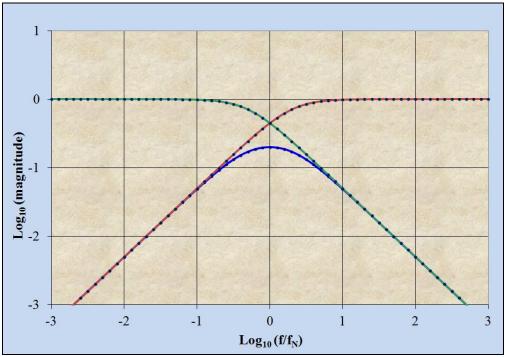

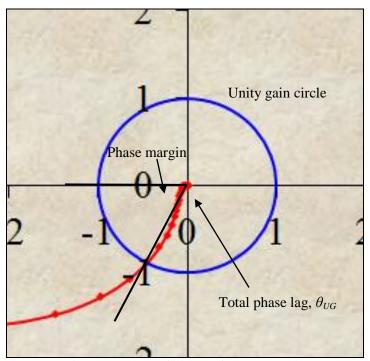

- 2.3 Phase margin

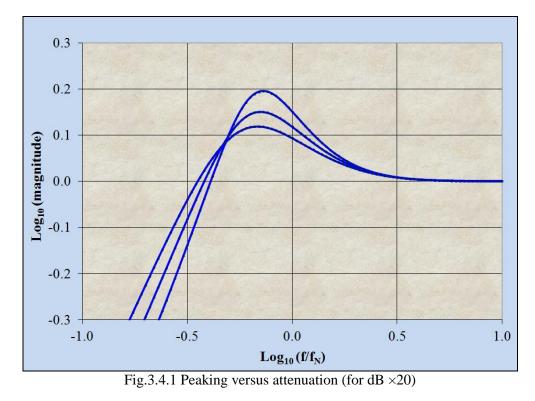

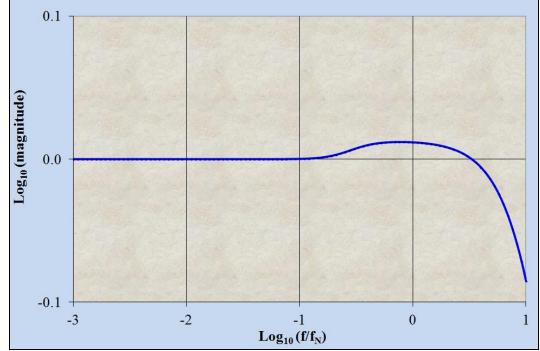

- 2.4 The size of the resonant peak

- 3. Some operational amplifier circuits

- 3.1 Operational amplifiers

- 3.1.1 Op-amp models

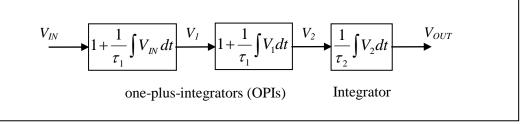

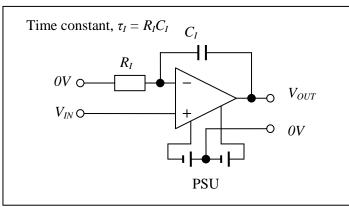

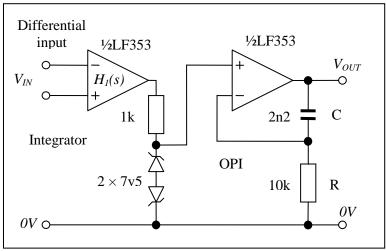

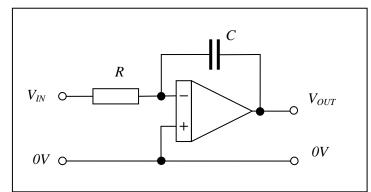

- 3.2 The integrator

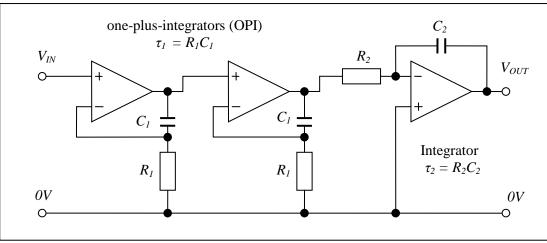

- 3.3 The one-plus-integrator (OPI)

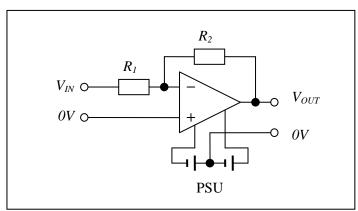

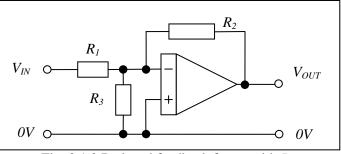

- 3.4 The non-inverting amplifier and voltage follower

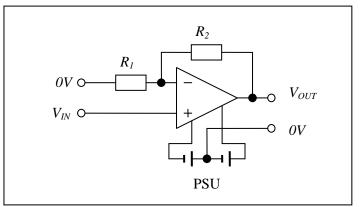

- 3.5 The inverting amplifier

- 3.6 A voltage follower with external compensation

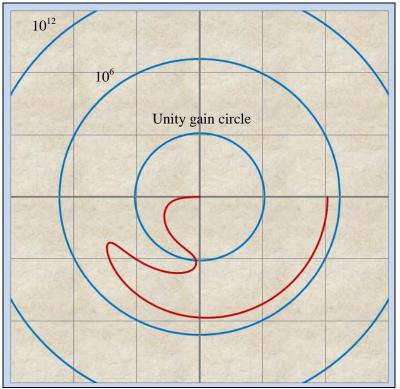

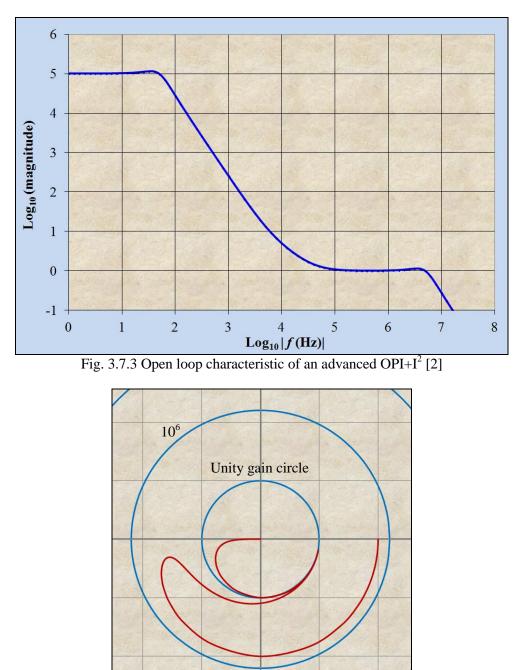

- 3.7 An advanced OPI<sup>2</sup>

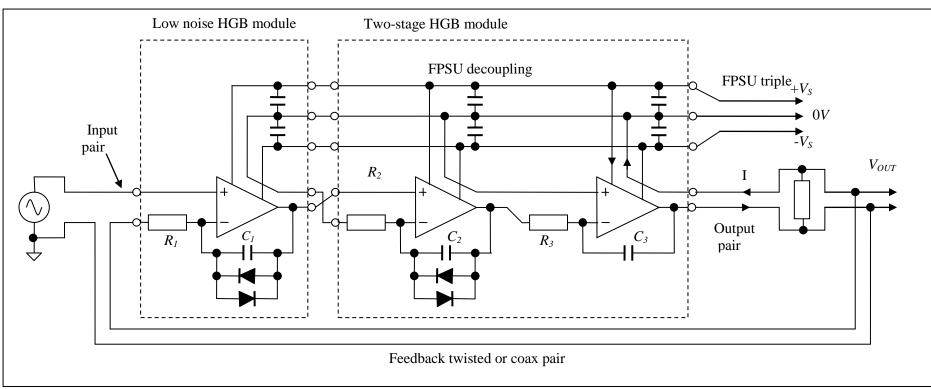

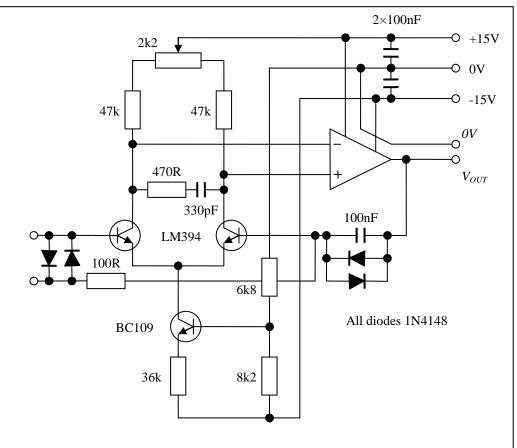

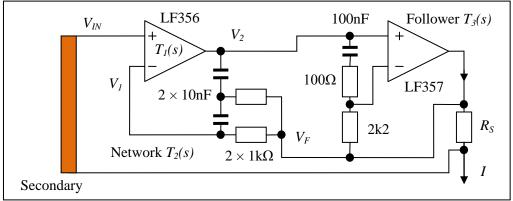

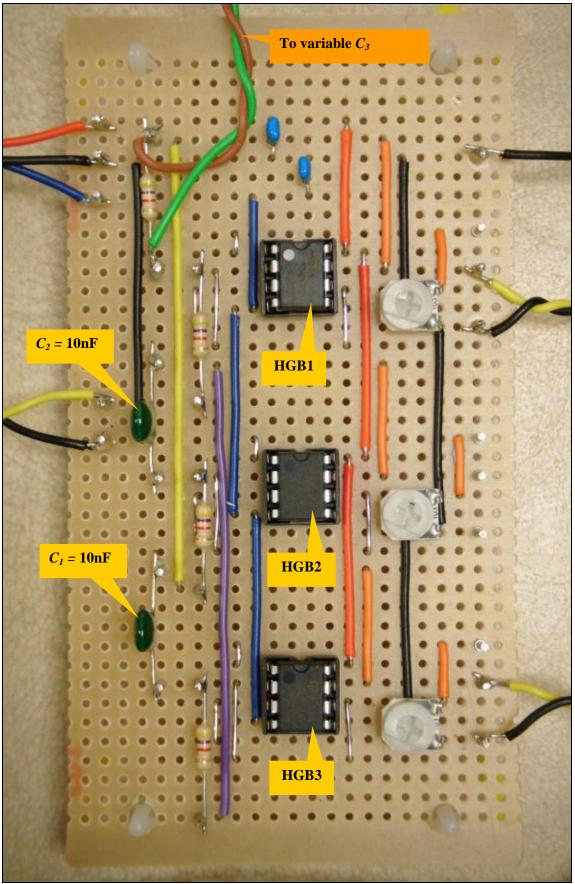

- 4. Multi-stage HGBs some practical circuits

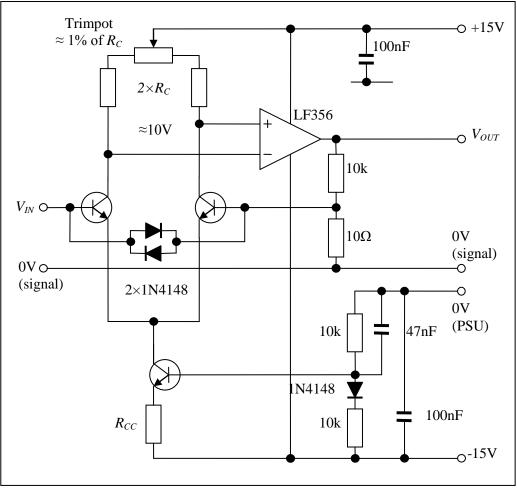

- 4.1 Type 1 HGBs

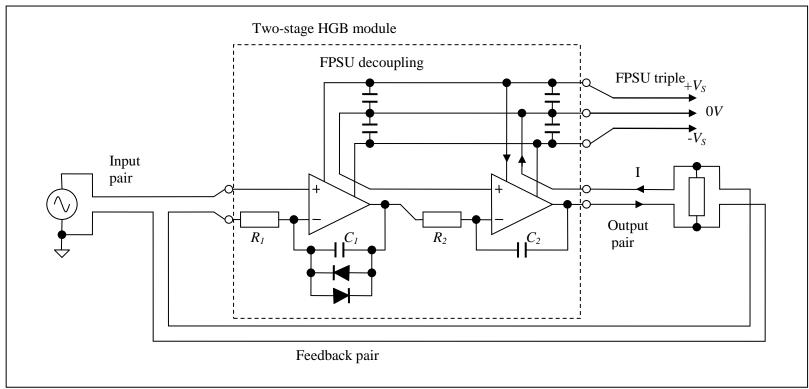

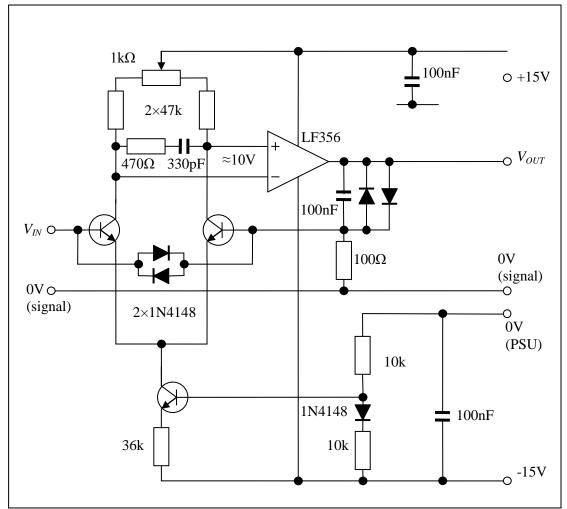

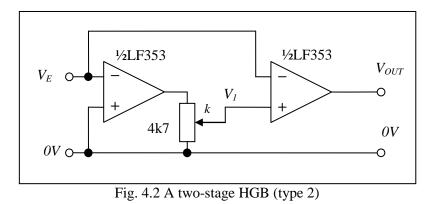

- 4.2 A type 2 two-stage HGB

- 4.3 A type 3 two-stage HGB

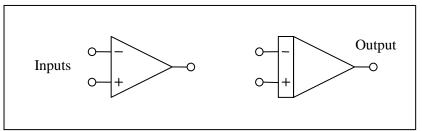

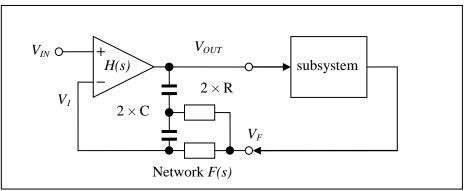

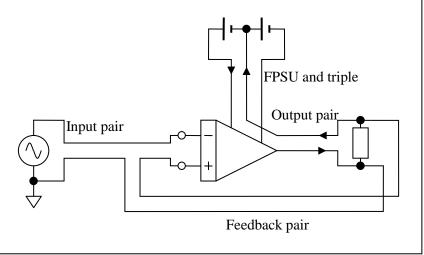

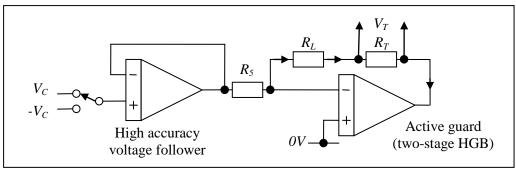

## Monograph 2: High accuracy voltage followers (HAVFs)

- 1. Introduction

- 2. Theory of operation

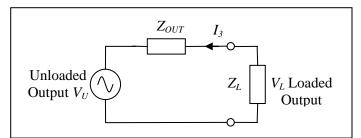

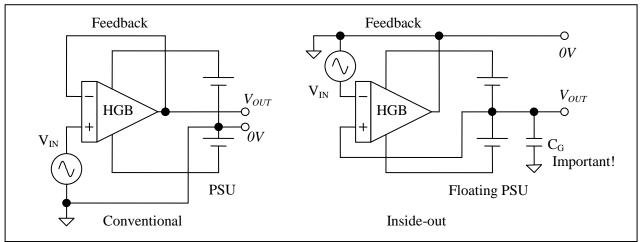

- 2.1 The limitations of a conventional voltage follower

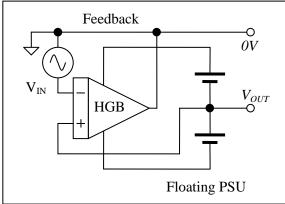

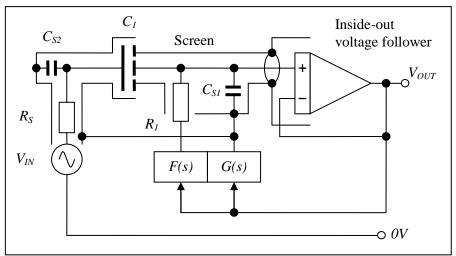

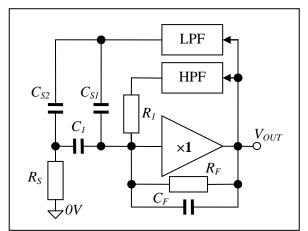

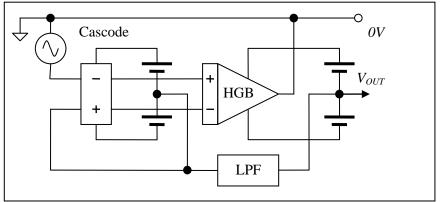

- 2.2 Common mode rejection and the "inside-out" configuration

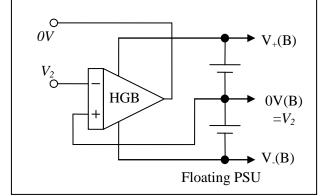

- 2.3 The floating power supply (FPSU)

- 2.4 Closed loop transfer functions

- 2.5 Error analysis

- 3. Power supply and signal wiring.

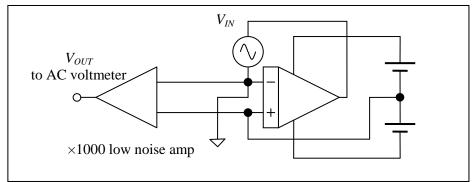

- 4. Measuring the accuracy of an inside-out follower

- 5. Stability considerations

- 6. Practical circuits

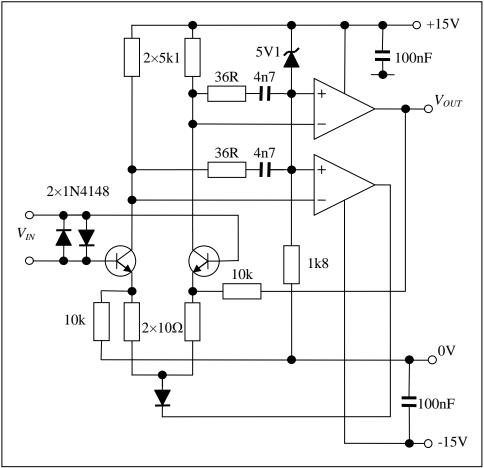

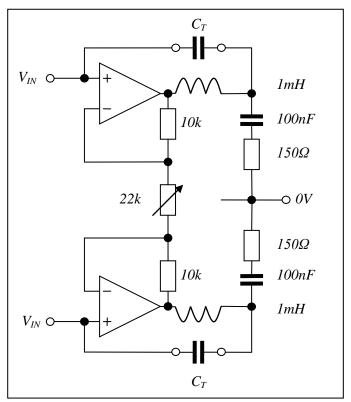

- 6.1 A two-stage HAVF

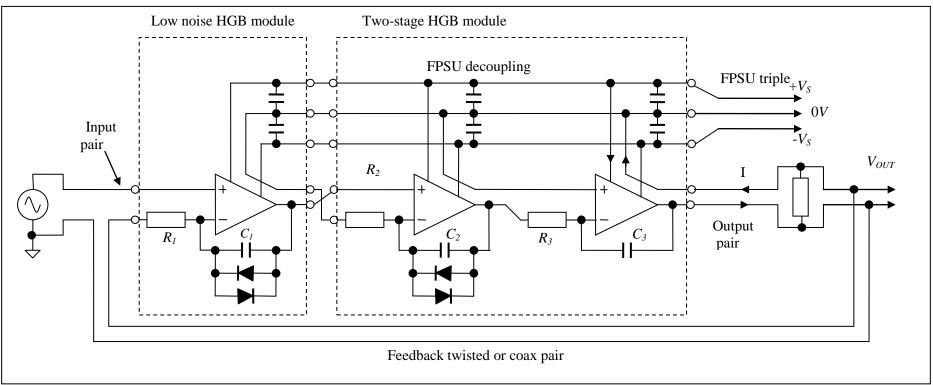

- 6.2 A three stage HAVF with low noise front end

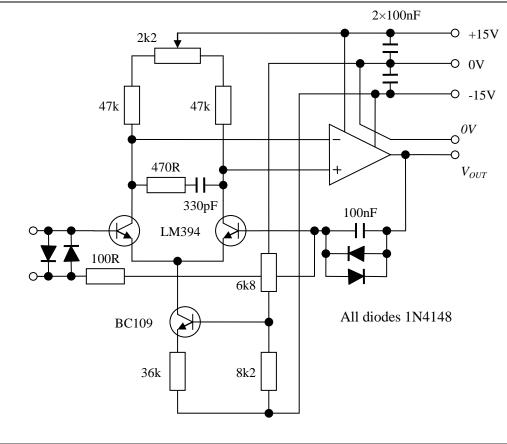

- 6.3 A low cost follower with moderately high accuracy

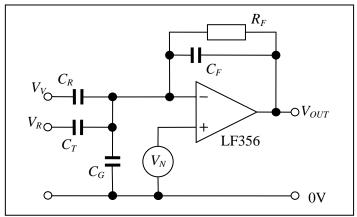

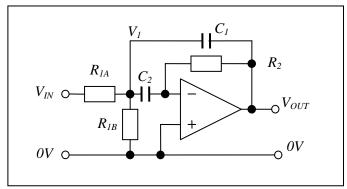

## Monograph 3: High accuracy amplifiers, integrators and differentiators

- 1. Introduction

- 2. General analysis

- 3. High accuracy amplifiers

- 3.1 The closed loop transfer function

- 3.2 Error analysis

- 3.3 Example calculation

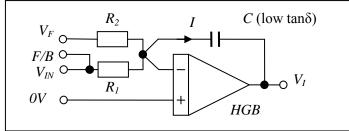

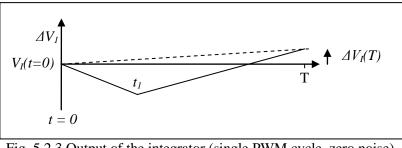

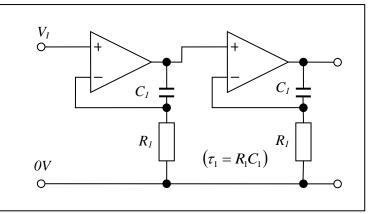

- 4. High accuracy integrators

- 4.1 The closed loop transfer function

- 4.2 Error analysis

- 4.3 Example calculation

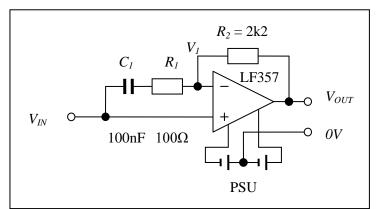

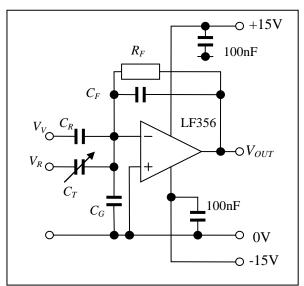

- 5. A high accuracy differentiator

- 5.1 The closed loop transfer function

- 5.2 Error analysis

- 5.3 Example calculation

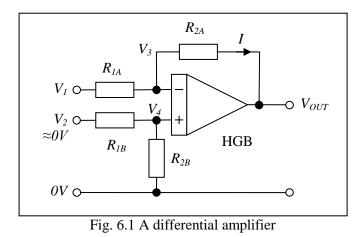

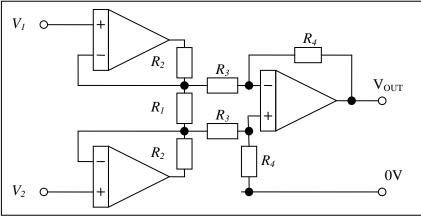

- 6. A high gain differential amplifier

- 6.1 The closed loop transfer function

- 6.2 Errors due to resistor tolerance

- 6.3 Example application and calculations

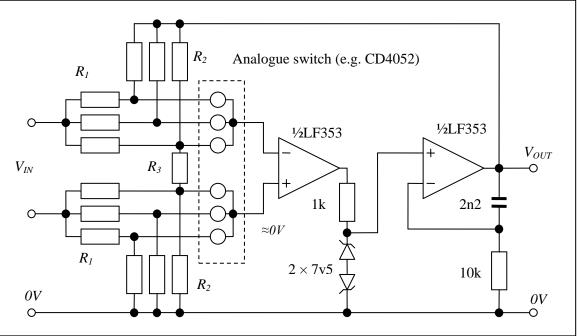

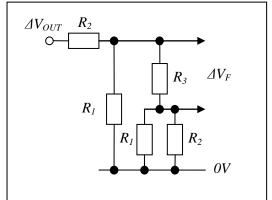

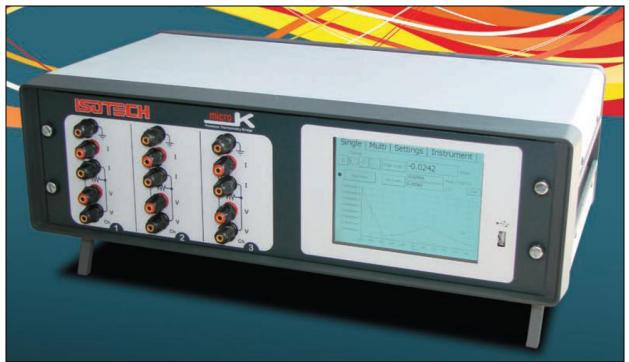

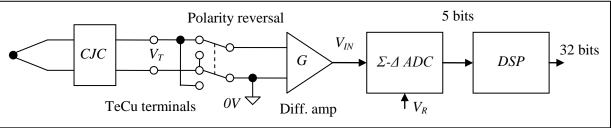

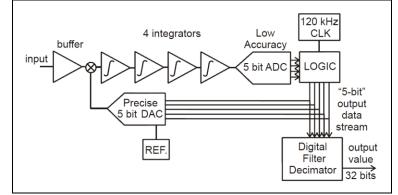

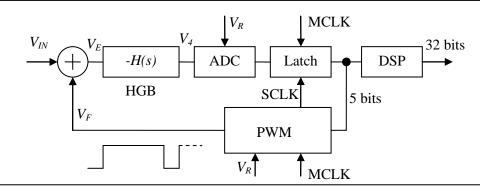

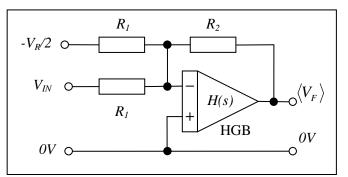

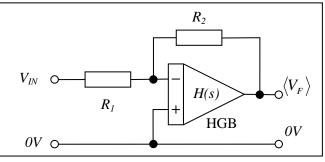

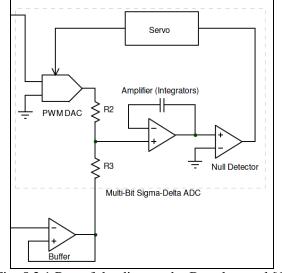

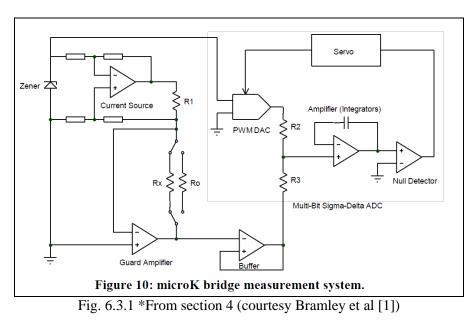

## Monograph 4: The Isotech microK "bridge"

- 1. Introduction

- 2. The microK measurement system (overview)

- 2.1 Introduction

- 2.2 Voltage (thermocouple) measuring mode

- 2.3 Resistance ratio measuring mode

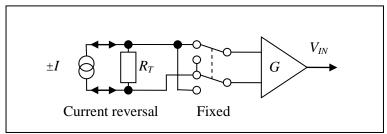

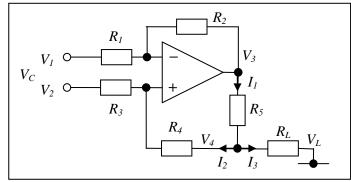

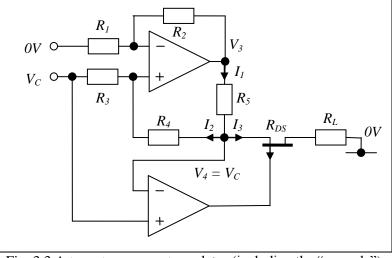

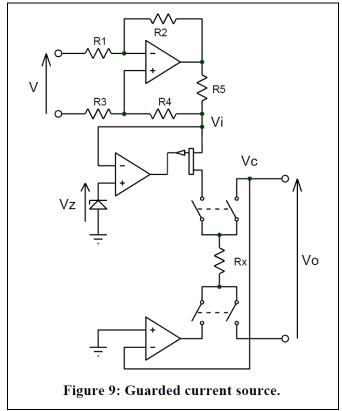

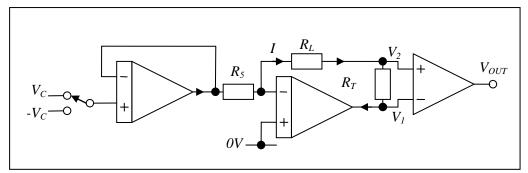

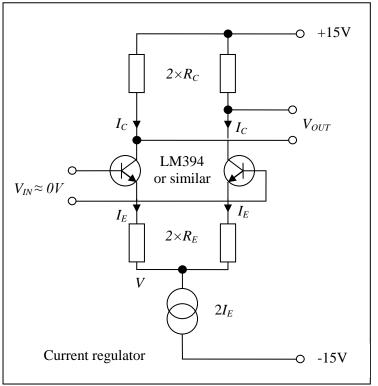

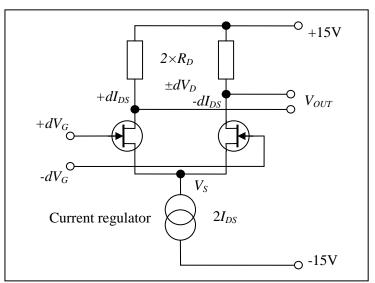

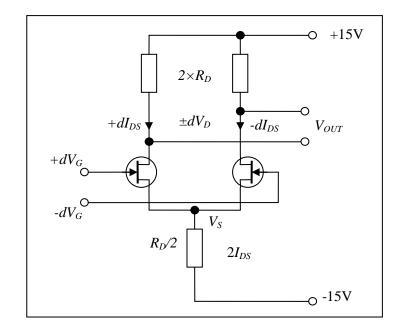

- 3. The voltage controlled (ultra-constant) current source

- 4. The differential amplifier

- 5. The sigma-delta ADC

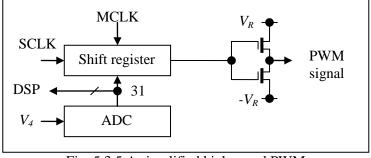

- 5.1 Overview

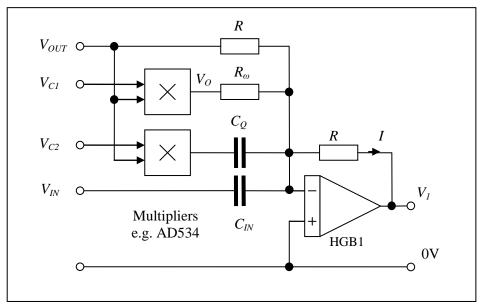

- 5.2 The summing junction and high gain block

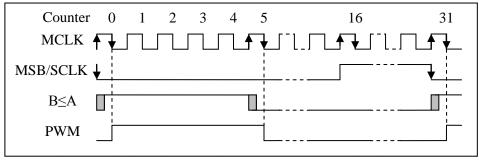

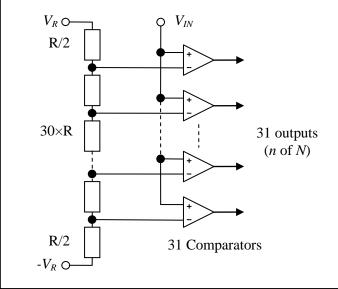

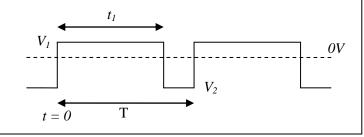

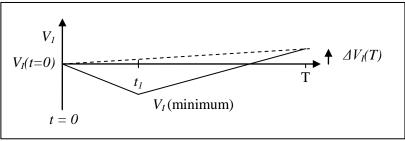

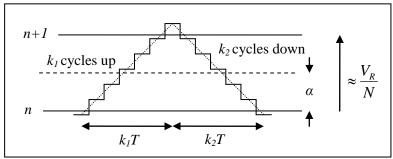

- 5.3 The flash ADC and pulse width modulator

- 6. Feedback and comment from Paul Bramley

- 6.1 Noise performance

- 6.2 Performance compared to conventional null balance bridges

- 6.3 Is it a bridge?

- 6.4 Timing accuracy

- 6.5 Reversal frequency and 1/f noise

- 6.6 Master reference voltage device

- 6.7 The differential amplifier

- 6.8 Elimination of amplifier offset and thermal emfs

- 6.9 The need for certain components to have very good short term stability

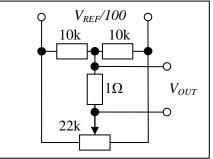

6.10 The measuring currents are proportional to a master internal reference voltage,  $V_{REF}$ , probably via a

- 12-bit multiplying digital to analogue converter

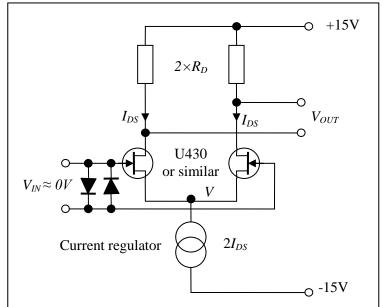

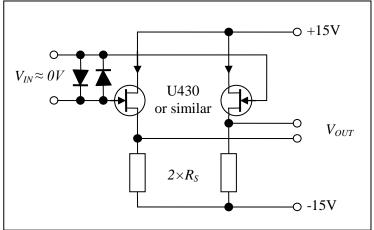

- 6.11 The current regulator

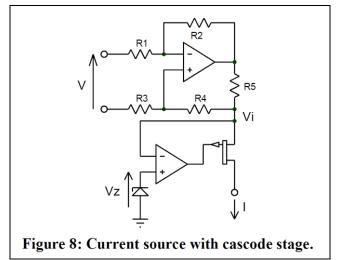

- 6.12 Is the current regulator second stage a "cascode" stage?

- 6.13 Suggested alternative design (Fig. 3.7): -

- 6.14 The differential amplifier

- 6.15 Bootstrapped PSU

- 6.16 The ADC

- 6.17 Further comments from PB

Appendix: More analysis of the microK sigma-delta ADC

work in progress: -

Monograph 5: Multislope ADCs

## Part 5: Null detector circuits

## Monograph 1: Null detectors - the basics

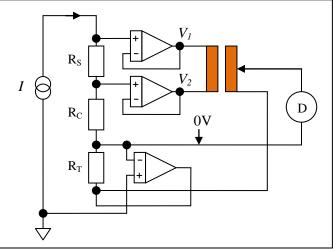

1. Introduction

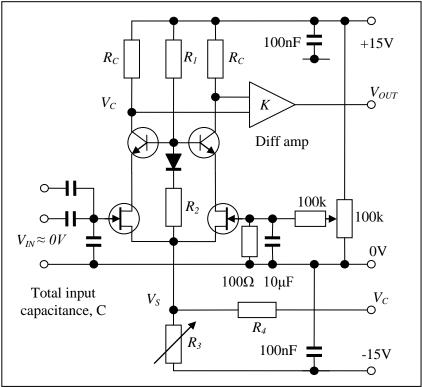

- 2. Low noise pre-amps

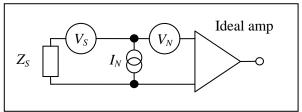

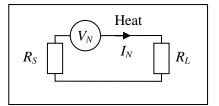

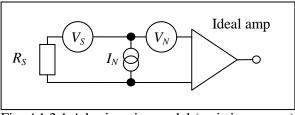

- 2.1 A basic pre-amp noise model

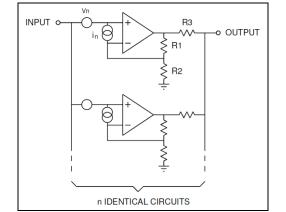

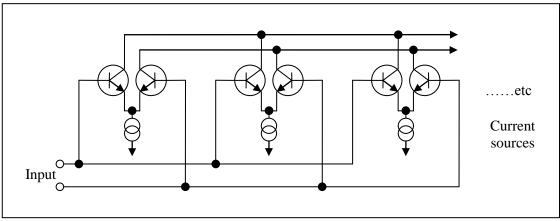

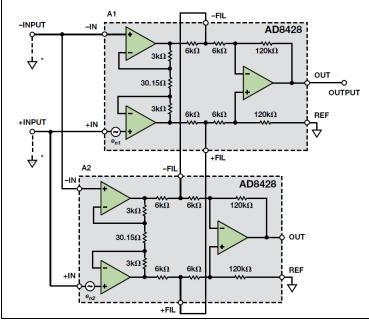

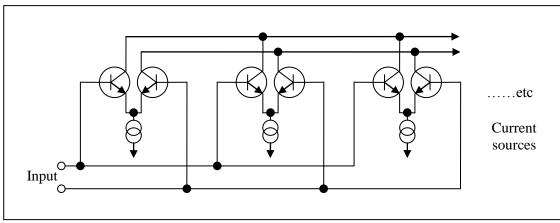

- 2.2 Amplifiers in parallel

- 2.3 Noise matching transformers

- 2.4 Charge amplifiers

- 2.4.1 Example calculation

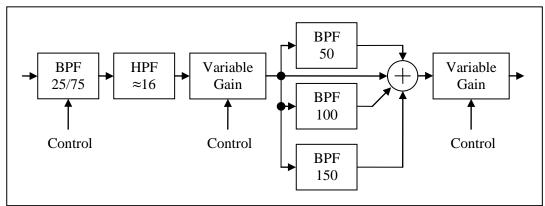

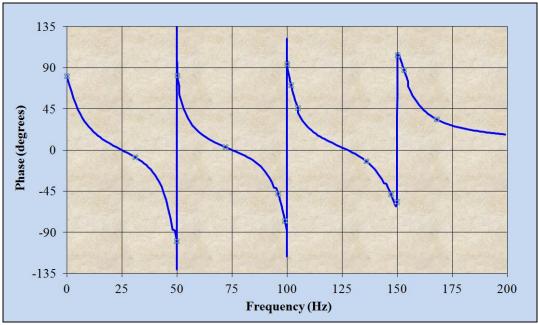

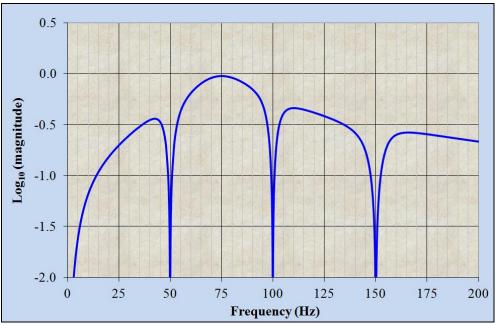

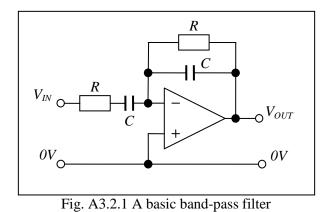

- 3. AC gain and filtering

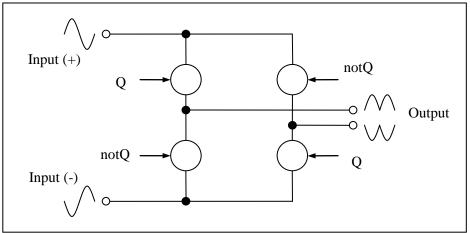

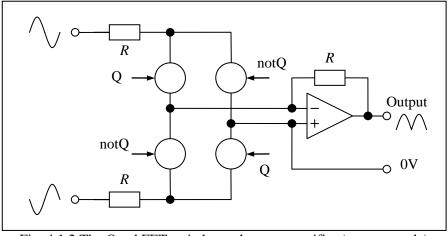

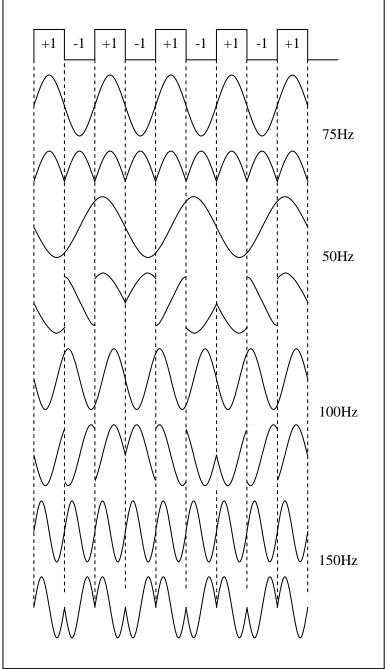

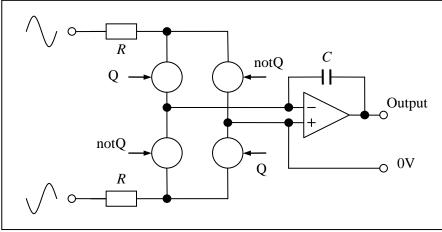

- 4. Synchronous rectifiers

- 4.1 The quad FET switch

- 4.2 Rejection of Noise and Interference

- 4.3 Output ripple

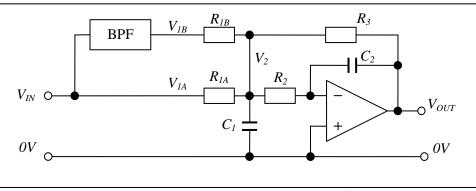

- 5. Low-pass filters

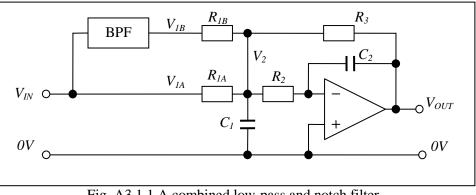

- 5.1 A combined low-pass/notch filter

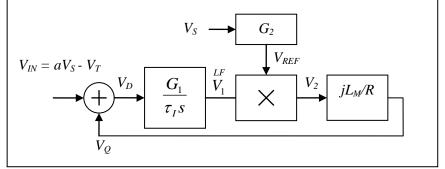

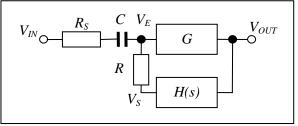

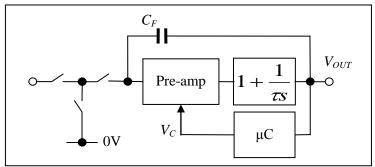

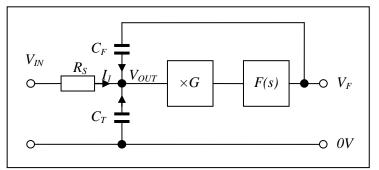

- 5.2 A bridge as part of a control system

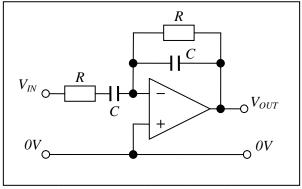

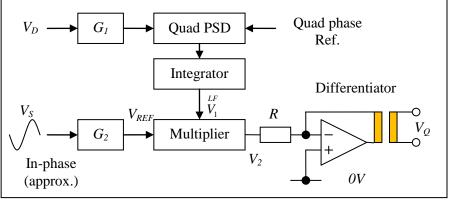

- 6. The quadrature servo

- 6.1 In-phase and quadrature

- 6.1.1 Example calculation: -

- 6.2 A practical quadrature servo

- 6.3 The servo as a control loop

- Appendix 1: Basic noise theory

- A1.1. Johnson noise

- A1.2. Low noise pre-amps

- A1.3 Optimum noise matching

- A1.4. Some notes on Nyquist's theory

- Appendix 2: Band-pass filter analysis

- A2.1 The transfer function

- A2.2 Bandwidth

- Appendix 3: Low-pass/notch filter analysis

- A3.1 The basic low-pass filter

- A3.2 A basic band-pass filter

## Monograph 2: Low noise BJT pre-amplifiers

- 1. Introduction

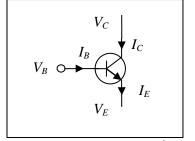

- 2. A review of basic BJT theory (low frequency)

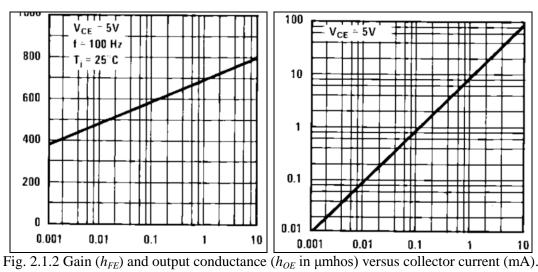

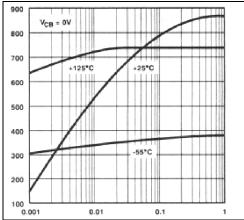

- 2.1 Current gain and output conductance

- 2.2 Base current

- 2.3 Emitter output resistance

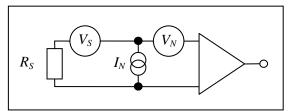

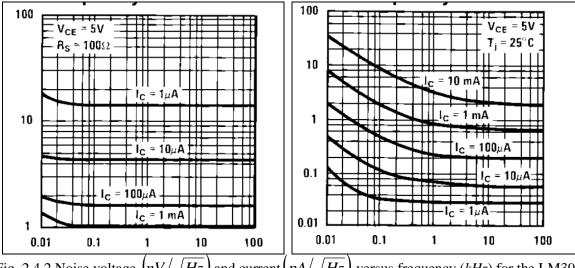

- 2.4 BJT noise performance

- 2.4.1 Example calculation

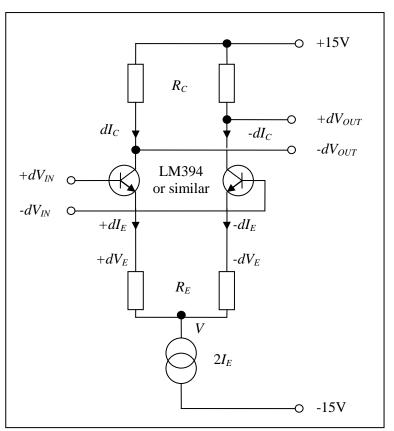

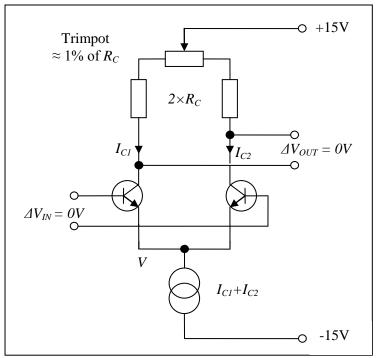

- 3. Analysis of the long tail pair

- 3.1 Voltage gain

- 3.1.1 Example calculation

- 3.2 Differential input resistance

- 3.3 Common mode rejection (mismatched resistors)

- 3.4 Common mode rejection (mismatched transistors)

- 3.5 Input offset voltage and temperature coefficient

- 4. Practical circuits

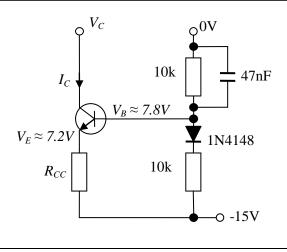

- 4.1 A basic current regulator

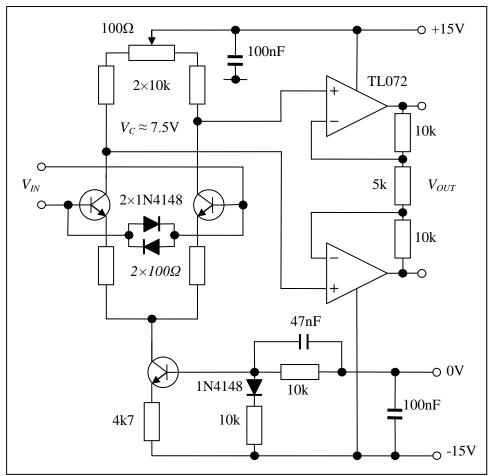

- 4.2 A fully differential pre-amp

- 4.3 A pre-amp with feedback

- 4.4 A low noise stage for an HAVF

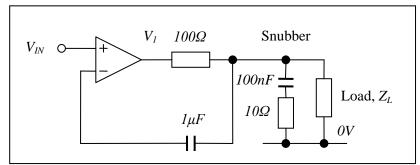

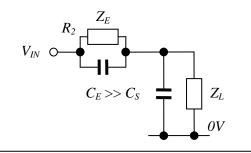

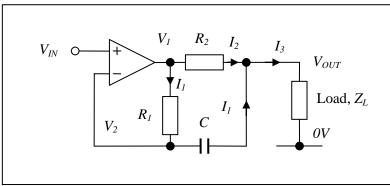

- 4.4.1 Stability and the snubber

4.5 A useful variant

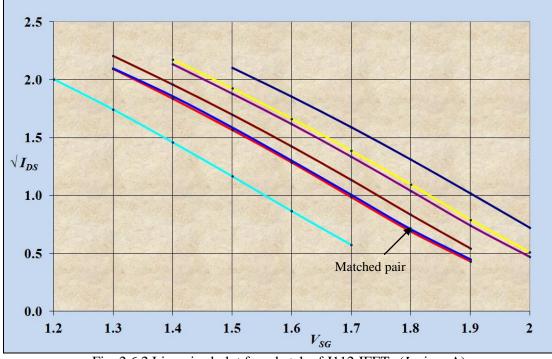

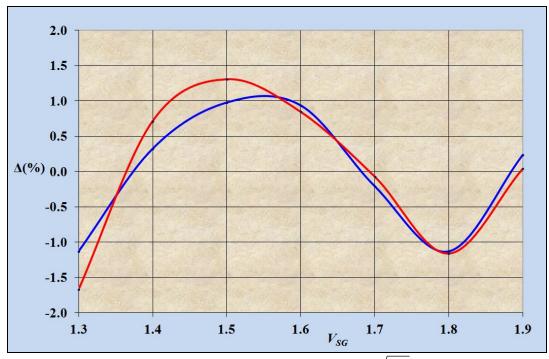

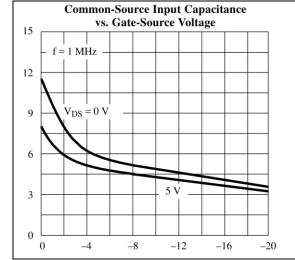

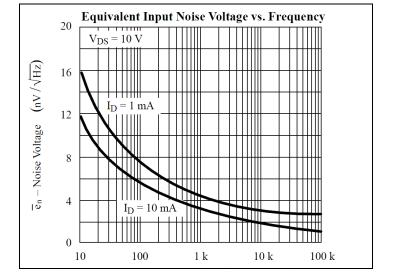

## Monograph 3: Low noise JFET pre-amplifiers

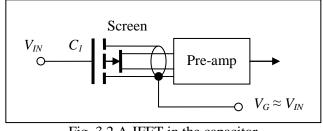

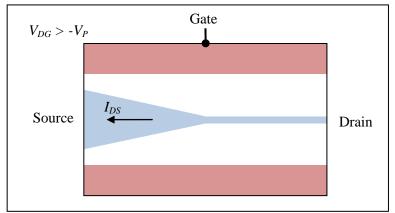

- 1. Introduction

- 2. The long tail pair

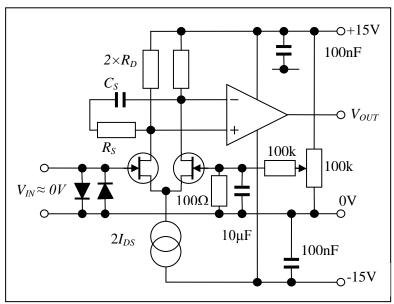

- 3. A differential source follower4. An ultra-low input current pre-amplifier

- 4.1 Example calculation

- 5. Charge amplifiers

- 5.1 Op-amp based charge amplifiers

- 5.2.1 Example calculation

- 5.2 A charge amplifier with long tail pair front end

- 5.3 A charge amplifier with source followers.

- 5.4 An ultra-low leakage charge amplifier

- 6. Transducers incorporating a charge amp or single JFET

- Appendix: Long-tail pair theory

- A1. Voltage gain

- A2. Common mode rejection ratio

- A2.1 Mismatched drain resistors

- A2.2 Mismatched JFETs

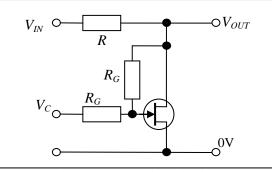

- A3. The long-tail pair in VCR mode

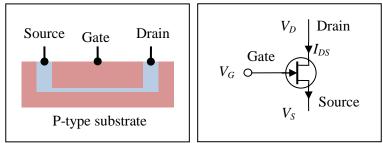

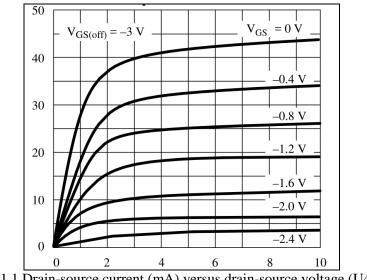

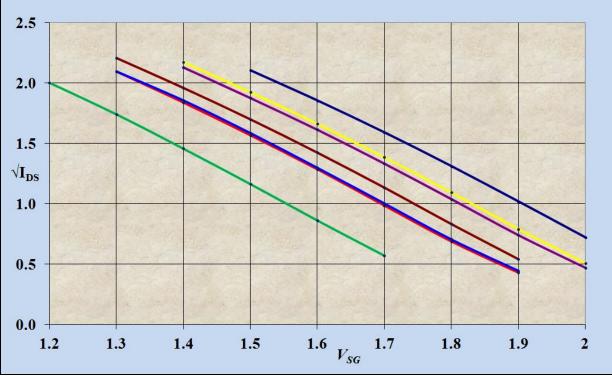

## Monograph 4: JFET theory

- 1. Introduction

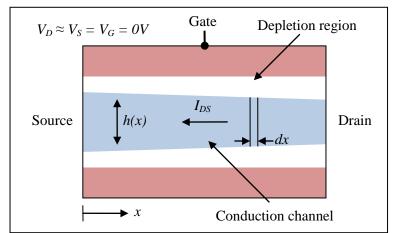

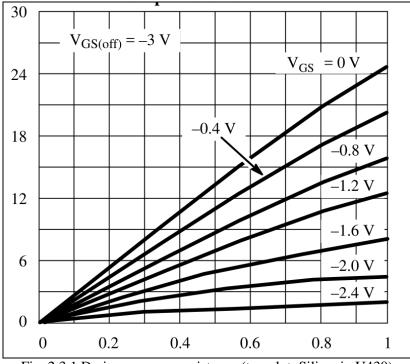

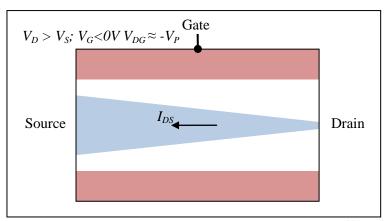

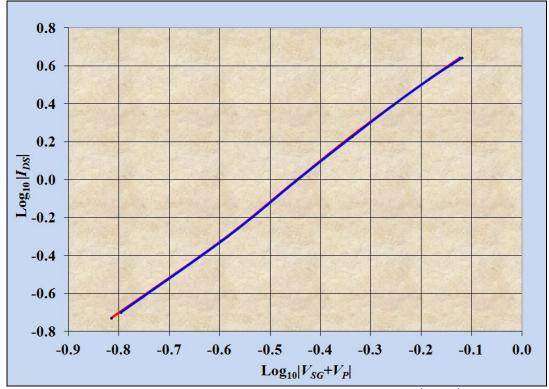

- 2. The theory

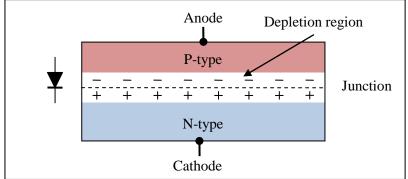

- 2.1 Basic theory of the PN junction

- 2.2 The model

- 2.3 Drain-source on resistance

- 2.4 Voltage controlled resistor mode

- 2.5 The general case

- 2.6 Pinched-off mode

- 2.7 Deviation from the model

- 2.8 Design rules of thumb

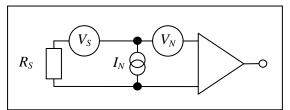

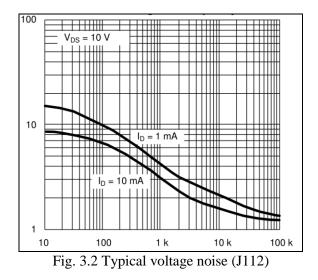

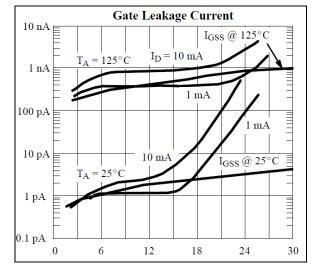

- 3. JFET noise performance

- 3.1 The basic model

- 3.2 Noise performance

## Part 6: Miscellaneous circuits

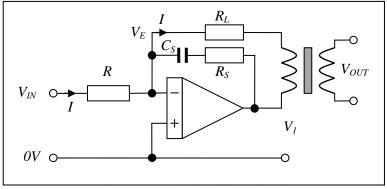

## Monograph 1: A simulated large capacitor circuit

- 1. Introduction

- 2. Basic analysis

- 3. Errors due to limited gain-bandwidth product

- 4. Practical considerations

- Appendix 1: Error analysis (due to limited gain-bandwidth product)

Appendix 2: Snubber example calculations

## Monograph 2: A simulated negative capacitor circuit

## 1. Introduction

- 1.1 The scale of the problem

- 2. Basic circuit analysis

- 3. A circuit with a simple first order filter

- 3.1 Example calculation

- 4. A circuit with a two-stage filter

- 4.1 Example calculation

- 4.2 A check on the output impedance

- 4.3 A practical circuit

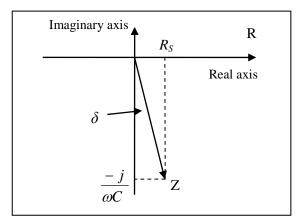

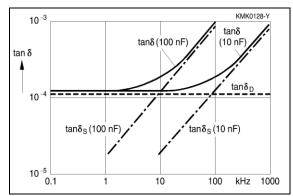

## Monograph 3: A circuit for measuring tanð.

## 1. Introduction

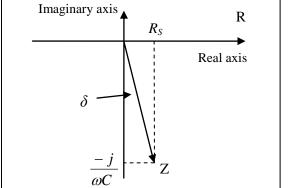

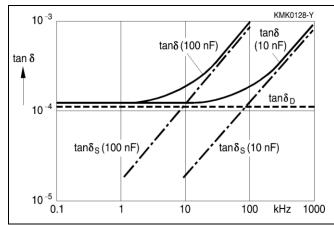

- 1.1 The general complex representation

- 2. A practical circuit

- 2.1 Analysis of the borderline oscillator circuit (BOC)

- 2.2 Results (sustained oscillation method)

- 2.3 Results (decaying sinusoid method)

- 3. Some nice maths

- 4. A prototype

- 5. A voltage controlled high Q filter/oscillator

- 6. Compensating for tanδ

## High accuracy resistors

## 1. Introduction

The world's most accurate resistors are based on the (cryogenic) quantum Hall effect and beyond the scope of this collection. Fortunately it is possible to construct practical (room temperature) resistors and resistive sensors which obey Ohm's law (within limits) with an accuracy approaching 1ppb. For the highest accuracy, however, operating temperature must be controlled (including self-heating) to within  $\pm 0.01^{\circ}$ C or better.

High accuracy resistors are constructed in three principal ways, depending on the resistor value and the length of the connecting leads. The main issues are resistance and capacitance of the connecting leads, series inductance of the resistor and the importance of phase error for the particular application: -

The three types are: -

- 1. Single-terminal-pair (1TP, sometimes referred to as "two-terminal-pair" resistors [1]).

- 2. Two-terminal-pair connection (2TP, sometimes referred to as "four-wire" or "Kelvin" connection).

- 3. Four-terminal-pair connection (4TP).

The first method is appropriate for high value resistors where the lead resistance is negligible. Parallel capacitance and electrical interference may be a problem in which case the resistor and connections need to be screened. The main application is transfer standards and high accuracy circuits (e.g. amplifiers, integrators and oscillators).

The second method is appropriate for low to medium value resistors where the lead resistance is significant. One pair delivers the current while the other pair is used to measure the voltage. Bridge techniques can distinguish between the in-phase and quadrature (real and imaginary) components of impedance and a small phase error (e.g. due to parallel capacitance of the leads or series inductance) is not usually a problem. Clearly, however, the size of the problem increases with frequency and high accuracy resistors and measurement techniques are designed to operate at low (or very low) frequency (sinewave or alternating DC). Very low frequency measurement is severely limited by thermal emfs and 1/f noise and so low frequency (10Hz - 1kHz) sine wave methods remain popular. The main applications are transfer standards and resistance thermometry.

Fig. 1.1 The "Wilkins" type transfer standard 2TP resistor (designed for immersion in a temperature controlled bath of mineral oil - courtesy ASL U.S.)

The third type is the ultimate method, for the very highest accuracy, reducing the effect of lead capacitance. The main application is for medium to high value transfer standards.

1. Awan, S., Kibble, B., and Schurr, J: "Coaxial Circuits for Interference-free Measurements" Electrical Measurements Series 13 published by the IET. <u>www.theiet.org</u>. For a different perspective see chapter 5 "General Principles of Accurate Impedance Measurement". For "two-terminal–pair" see section 5.3.6.

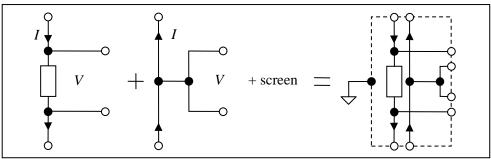

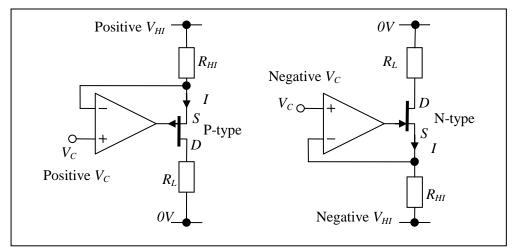

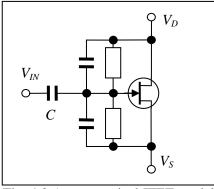

## 2. Single-terminal-pair plus screen

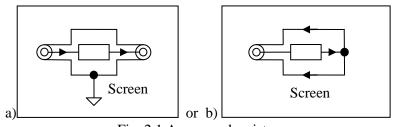

If the resistance value is high, compared to the connecting leads, then a single pair of connections is all that is required. Interference from electric and magnetic fields can be an issue but a screen around the resistor (fig. 2.1a) and coaxial connections provide a simple solution (see, also, fig.2.4). It can easily be arranged that the screen/outer conductor is at local 0V, at least approximately, with low impedance to "earth" (fig. 2.1a). The screen can also provide the route for the return current in order to minimise external magnetic flux - the electric and magnetic fields are contained within the coax cable (fig. 2.1b).

Fig. 2.1 A screened resistor

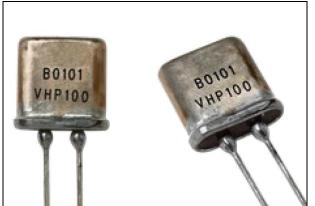

Commercially available miniature component resistors, while not quite matching the long term stability of the Wilkins type, have excellent temperature stability and AC characteristics. Single resistors, matched pairs and networks with an initial tolerance of  $\pm 0.01\%$  and temperature coefficients  $<1ppm/^{\circ}C$  (20-30°C) are readily available.

Fig. 2.2 High accuracy component resistors (picture courtesy Vishay Precision Group, Inc)

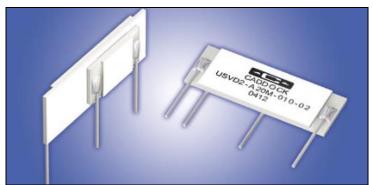

With pairs, triples and networks the accuracy and stability of ratio can be even better: -

Fig. 2.3 High accuracy 100:1 ratio resistor pair (courtesy Caddock Inc.)

The main applications are transfer standards and accurate amplifiers and integrators [1].

1. Part 4, Monograph 3: "High accuracy amplifiers, integrators and differentiators".

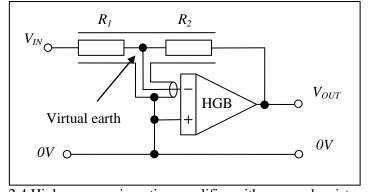

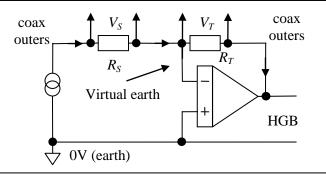

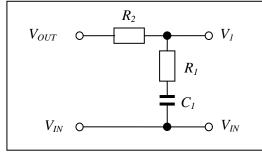

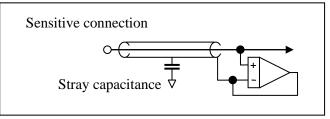

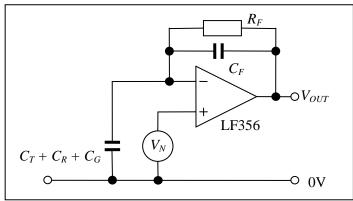

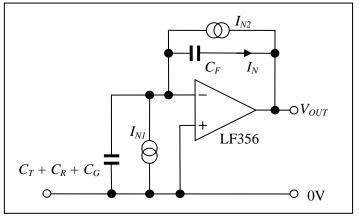

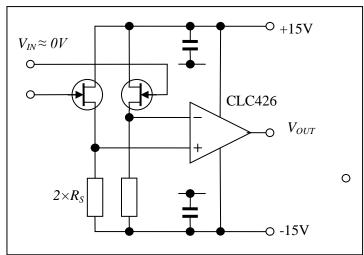

One simple method for eliminating the effect of interference and stray capacitance (across the resistor) is to connect one terminal to a virtual earth with the screen connected to 0V. An overall 0V screen around the high gain block front-end may also be necessary: -

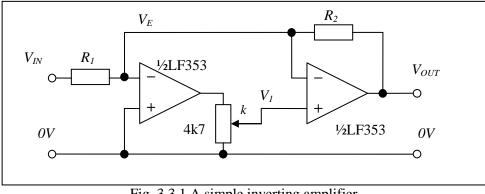

Fig. 2.4 High accuracy inverting amplifier with screened resistors [1]

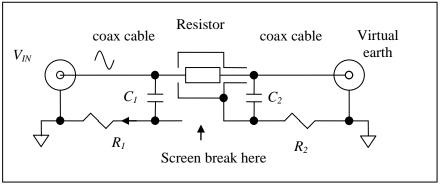

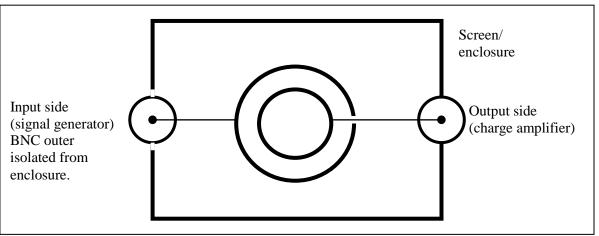

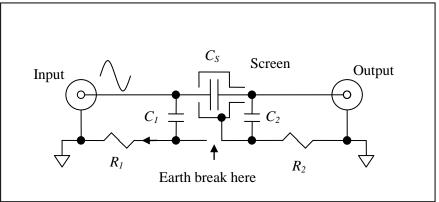

If the resistor is at the end of a pair of coaxial cables the outer conductors (screens) should not be connected together at the resistor end. If they are connected the current flowing through  $C_1$  (signal input side) can develop a small voltage drop down the screen resistances ( $R_1$  and  $R_2$  in parallel) which then injects an in-phase current\* into the virtual earth via the cable capacitance  $C_2$ : -

Fig. 2.5 Simplified equivalent circuit of a remote resistor

Magnetic interference can be kept to a minimum by routing a pair of coaxial cables together as a twisted pair. Any stray AC magnetic flux passing through a loop formed by the cables induces a voltage which is added in series with the resistor. Thin and flexible coax cable with a less than perfect screen (c.f. earphone cables) may be better, in practice, than the more usual kind of high quality (less flexible) type. The twisted pair could always be routed through a flexible metal conduit, connected to local 0V, if electric field interference is a particular problem.

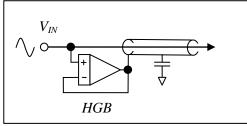

\*Such a current can also be eliminated with a high accuracy voltage follower/active guard [2]: -

Fig. 2.6 An active guard circuit

(Caution – this method involves an amount of positive feedback, depending on  $V_{IN}$  source resistance)

- 1. Part 4, monograph 3: "High accuracy amplifiers, integrators and differentiators".

- 2. Part 4, monograph 2: "High accuracy voltage followers (HAVFs)". See section 1.

## 2.1 Converting a single to a four-terminal-pair resistor

For the very highest accuracy some experts advise that the effect of lead resistance can be significantly reduced by adding coaxial T-connectors physically close to the device [1]. This is then "regarded" as a four-terminal-pair resistor. The result is described as a complex network (fig. 2.1.2), conforming to the generally accepted definition, though they do not include the resistance of the screen in the diagram. This must be included, therefore, in the defining parameter Z (see section 5).

Fig. 2.1.1 Converting a 1TP plus screen into a 4TP (courtesy Awan et al)

Fig. 2.1.2 Equivalent circuit of fig. 2.1.1 (courtesy Awan et al)

This author begs to differ!

1. The device in fig. 2.1.1 is, in effect, a two-terminal-pair resistor with screen (see the next section).

2. It is far better to break the screen connection thus avoiding the problem cited in the previous section. The return current is best routed via another conductor.

3. If it is unavoidable that the screen must carry the return current then it is important that the screen/connector resistances are as small as possible.

4. If the manufacturers don't know any better the experts should advise them accordingly.

A more satisfactory definition of a four-terminal-pair is offered in section 5.

This topic and the issues of "earth loops" and "chokes" are explored in the monograph "Coax AC bridges" [2]

1. According to Awan et al (see footnote page 1): "Many standard impedances made and sold for measurements of the highest accuracy have two-terminal-pair terminations, and no information is available for the length or impedance and shunt admittance of the internal cables between the impedance itself and these terminations. To improve their electrical definition, T-connectors can be added at the terminations. The impedance can then be regarded as being defined as a four terminal pair having its internal defining points at these T-connectors."

2. Part 3, monograph 9: "Coaxial AC bridges".

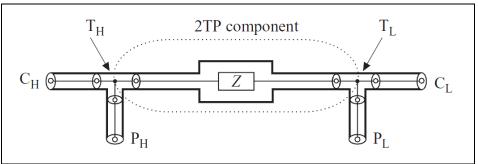

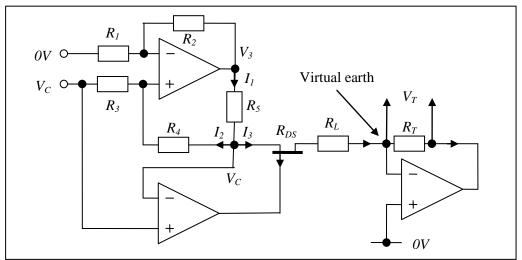

#### 3. Two-terminal-pair resistors

Most applications are for low to medium resistance measurement  $(1 - 1000\Omega)$ . Lead resistance is not negligible and so an extra pair of voltage sensing connections is required. The effect of resistance in the current carrying pair is eliminated as long as the current flowing in the voltage sensing leads is negligible. In most applications the effect of resistance in the connecting leads is insignificant and so they are not usually shown: -

Fig. 3.1 2TP connections

For high accuracy each pair needs to be co-axial or tightly twisted. This ensures that the magnetic flux transmitted from the current carrying pair and the voltage induced in the voltage sensing pair by any stray flux are kept to a minimum.

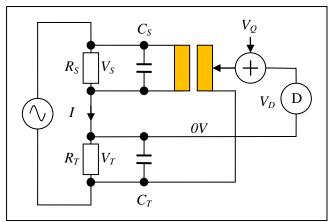

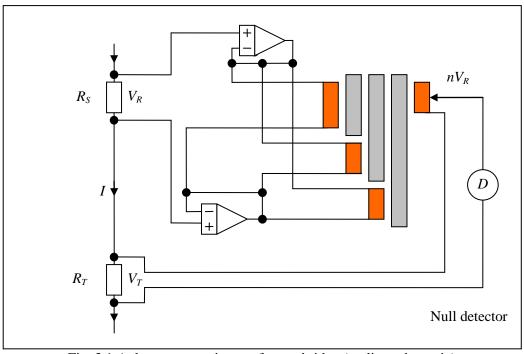

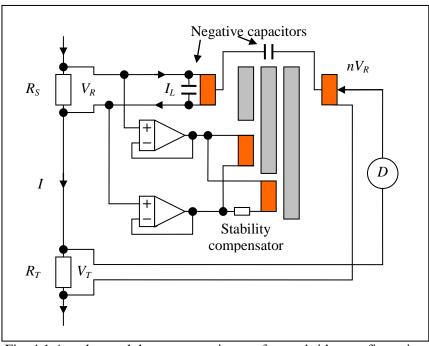

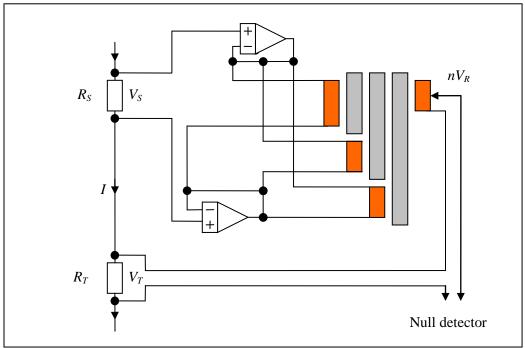

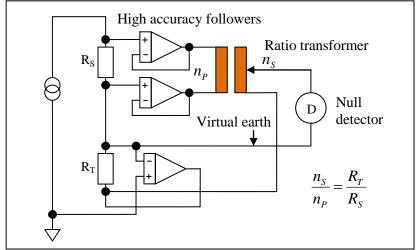

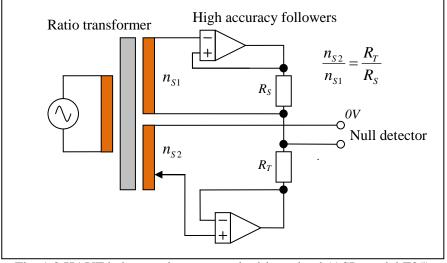

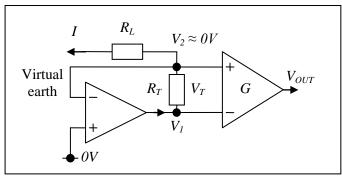

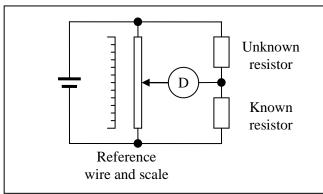

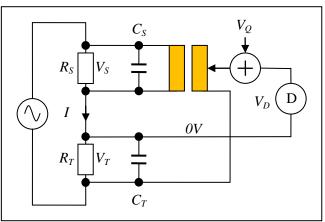

A typical bridge configuration is to use some kind of multiplier with sufficiently high input impedance (e.g. an actively energised ratio transformer). The null balance ensures that no current flows in the voltage connections from  $R_T$ : -

Fig. 3.2 A typical bridge configuration for 2TP resistors

The main issue with two-terminal-pair resistors is the effect of parallel capacitance. One metre of coaxial or twisted pair cable typically represents 100pF of capacitance. The two pairs act in parallel and so the total capacitance is roughly 200pF per metre of connecting cable.

The real part (in-phase) is balanced by the main ratio device – usually a very accurate ratio transformer or similar. The imaginary part (quadrature) is relatively small and balanced by a quadrature servo [1].

<sup>1.</sup> Part 5, monograph 1: "Null detectors - the basics".

#### 3.1 Analysis of parallel capacitance with quadrature balance

The quadrature servo adds a signal to the output of the ratio transformer so that a null is achieved to both in-phase and quadrature components: -

$$V_D = aV_S - V_T + V_Q = 0$$

$a = \frac{N_s}{N_p}$  is the transformer ratio setting. The phase error of a ratio transformer is usually much smaller than that due

to the parallel capacitance and is simply added to it – equivalent to a small change in the capacitance. The second order term (in-phase error) is negligible. One can assume, therefore, that a is a real number.

It is shown elsewhere [1] that a practical approach is to derive the quadrature servo signal from  $V_S$ : -

$$V_Q \approx jbV_S \implies V_D = (a+jb)V_S - V_T$$

$V_D = 0 \implies \frac{V_T}{V_S} = a+jb$

Define parameters:  $\theta_s = \omega_c R_s C_s$  and  $\theta_T = \omega_c R_T C_T$ . Both are small (typically <0.1mrad or 100ppm).

With a little algebra:

$$a + jb = \frac{R_T}{R_S} \times \frac{1 + j\theta_S}{1 + j\theta_T} \implies a = \frac{R_T}{R_S} \left(\frac{1 + \theta_S \theta_T}{1 + \theta_T^2}\right) \text{ and } b = \frac{R_T}{R_S} \left(\frac{\theta_S - \theta_T}{1 + \theta_T^2}\right)$$

Values for the quadrature components are typically <100ppm so that the effect on accuracy can be reduced to less than 10ppb.

For the very highest accuracy it is quite simple to add capacitance or, better still, matching cable to one side or the other so that the quadrature imbalance is reduced to almost zero. To a very good approximation, therefore: -

$$\theta_{s} \approx \theta_{T}$$

and  $\theta_{s} \ll 1$  and  $\theta_{T} \ll 1 \implies a \approx \frac{R_{T}}{R_{s}}$  and  $b \approx \frac{R_{T}}{R_{s}} (\theta_{s} - \theta_{T})$

Matching cable is the better choice because any loss factor ("tan( $\delta$ )") of the dielectric, equivalent to a small imaginary component for both  $\theta_s$  and  $\theta_r$ , is the same for both numerator and denominator.

$$\theta_{s} = \theta_{T} \text{ and } \theta_{s} \to \theta_{s}(1+j\delta) \text{ and } \theta_{T} \to \theta_{T}(1+j\delta) \implies a = \frac{R_{T}}{R_{s}}$$

#### 3.1.1 Example calculation: -

$R_s = 25\Omega$  with 1 metre of cable  $(C_s = 200 \, pF)$ ;  $R_T = 100\Omega$  at the end of 5 metres of cable  $(C_T = 1nF)$  at an operating frequency of 75Hz ( $\omega = 2\pi f = 471$  radians per second).

$$\theta_{\rm s} = 471 \times 25 \times 2 \times 10^{-10} \approx 2.4 \times 10^{-6}$$

$\theta_{\rm T} = 471 \times 100 \times 10^{-9} \approx 4.7 \times 10^{-5}$

$$\frac{\delta a}{a} \approx 2.2 \times 10^{-9}$$

(2.2ppb and negligible)

1. Part 5, monograph 1: "Null detectors – the basics". See section 6.1.

#### 3.2 Analysis of parallel capacitance without quadrature balance

One of the main reasons for a quadrature balance is the necessity for filtering in the null detector. This usually consists of a band pass filter at the operating frequency combined with notch filters at power supply frequency harmonics. The filtering can introduce phase shift and any quadrature component in the out-of balance signal appears, at the phase sensitive detector, as an in-phase error. The result is an error in the in-phase balance. In less demanding applications, with low levels of both quadrature and interference expected, there may be no need for a quadrature balance, in which case any phase error in the null detector needs to be kept low, as the following analysis shows: -

Define the phase shift in the null detector:  $\theta_D$ . The effect is equivalent to multiplying the bridge output by the phase factor  $\exp(j\theta_D) = \cos(\theta_D) + j\sin(\theta_D)$ .

$$V_{OUT} = \left\{ \cos(\theta_D) + j \sin(\theta_D) \right\} \left\{ \frac{aR_1}{1 + j\theta_1} - \frac{R_2}{1 + j\theta_2} \right\}$$

The phase errors of the resistors are very small but the null detector phase error may not be negligible. One can make only the following approximation: -

$$|\theta_1|$$

and  $|\theta_2| <<1 \Rightarrow V_{OUT} \approx \{\cos(\theta_D) + j\sin(\theta_D)\}(aR_1(1-j\theta_1) - R_2(1-j\theta_2))\}$

The bridge ratio, *a*, is adjusted so that the real part is zero.

$$\operatorname{Re}(V_{OUT}) = 0 \qquad \Rightarrow \qquad aR_1 \{\cos(\theta_D) + \theta_1 \sin(\theta_D)\} - R_2 \{\cos(\theta_D) + \theta_2 \sin(\theta_D)\} = 0$$

$$a = \frac{R_2}{R_1} \times \left(\frac{\cos(\theta_D) + \theta_2 \sin(\theta_D)}{\cos(\theta_D) + \theta_1 \sin(\theta_D)}\right) = \frac{R_2}{R_1} \times \left(\frac{1 + \theta_2 \tan(\theta_D)}{1 + \theta_1 \tan(\theta_D)}\right)$$

The result is exact if the detector phase error is zero and/or if the resistor phase errors are the same.

To a useful degree of accuracy, assuming small phase errors: -

$$|\theta_1|, |\theta_2| \text{ and } |\theta_D| \ll 1 \implies a \approx \frac{R_2}{R_1} \times (1 + (\theta_2 - \theta_1)\theta_D)$$

The proportionate error is, therefore:

$$\frac{\delta a}{a} \approx (\theta_2 - \theta_1) \theta_D$$

#### **3.2.1 Example calculation**

If one uses the same example as above with a null detector phase error of about 0.1 radians: -

$$\theta_1 = -2.4 \mu rad$$

$\theta_2 = -47 \mu rad$  and  $\tan(\theta_D) \approx 0.1$

$\frac{\delta a}{a} \approx -4.5 \, ppm$

Clearly a bridge without a separate quadrature balance can only cope with a small amount of quadrature imbalance.

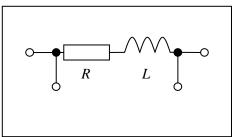

## 3.3 Quadrature due to series inductance

With low value resistors the problem is often the series inductance. Extra care needs to be taken in the construction of low value resistors to keep the self-inductance and mutual inductance (between the current carrying pair and the voltage sensing pair) as low as possible.

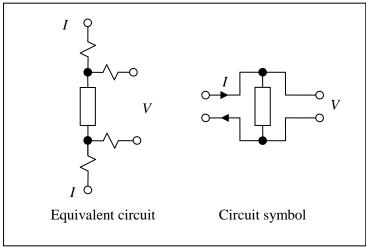

Fig. 3.3.1 Equivalent circuit

The impedance is:

$Z = R + j\omega L$

The phase error is now positive and inversely proportional to the resistance: -

$$\theta = \arctan\left(\frac{\omega L}{R}\right) \approx \frac{\omega L}{R}$$

in radians

The analysis is otherwise the same as with quadrature due to parallel capacitance.

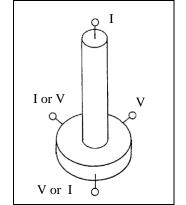

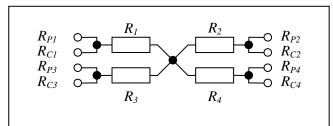

#### 3.4 Two-terminal-pair zero-Ohm junctions

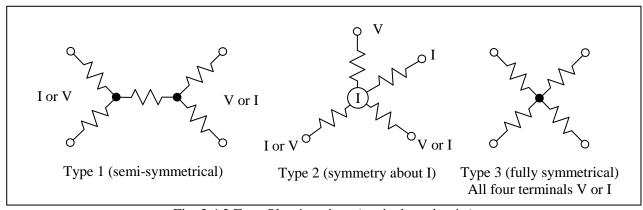

The basic idea of a zero-Ohm junction (ZOJ) is that current passing through one pair of connections results in negligible voltage developed across the other pair. In practice a junction resistance as low as a few n $\Omega$  is possible. They are useful in the construction of two-terminal-pair resistor networks (see section 4) and four-terminal-pair resistors (see section 5). The most basic type (type 1) is easy to construct (with bits of wire): The current carrying pair and the voltage sensing pair are physically separated by a low value resistor. The pairs are interchangeable  $(V \leftrightarrow I)$  but may not be mixed. Type 1 junctions are used in four-terminal-pair resistors.

Type 2 junctions, have one dedicated current and one dedicated voltage sensing terminal. The other two connections can be used for either current carrying or voltage sensing. A high degree of symmetry is required between the dedicated current terminal and the other three. The construction is typically a solid cylinder of copper for the dedicated current terminal with the other three connections emerging radially at 120 degree intervals. Type 2 junctions are used in series connected (Hamon type) networks. See section 4.3.1 for more detail.

Fig. 3.4.1 A type 2 zero-Ohm junction

Type three is fully symmetrical and requires much higher precision with regards to the (tetrahedral) symmetry of construction. The main advantage is that all four connections are interchangeable (i.e. can be used for current carrying or voltage sensing). Type 3 junctions are used in White/Jones type networks. See section 4.3.2 for more detail.

Fig. 3.4.2 Zero-Ohm junctions (equivalent circuits)

Good AC performance is achieved by ensuring, as near as possible, the voltage sensing pair is perpendicular to the current carrying pair and the areas are kept to a minimum thus minimising mutual inductance.

#### 4. Two-terminal-pair resistor networks

## 4.1 Introduction

Whereas connecting separately constructed two-terminal-pairs in parallel is possible it is not very practicable. This is demonstrated in the next section. Connecting two or more in series is virtually impossible if high accuracy is required. The solution is to construct two or more resistors with permanent series connections using zero-Ohm junctions. The small resistance of the junction connections forms part of the accurately defined resistor which is trimmed accordingly. The other two connections provide the means for measuring each individual resistor as a two-terminal-pair resistor.

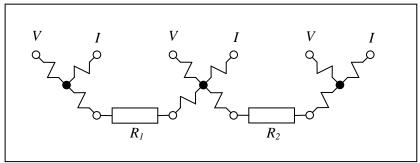

The main application is resistance bridge calibration with an accuracy approaching 10ppb (with accurate and stable temperature control) from DC to 400Hz AC. The following, for example, provides the means of producing three values of resistance ( $R_1$ ,  $R_2$  and  $R_1+R_2$ ). The latter can be calculated as well as measured.

Fig. 4.1.1 Two-terminal pair resistors in series

The basic idea of networks is that series and parallel combinations of two-terminal pair resistors can be calculated and measured with great accuracy. They provide a convenient means for comparing transfer standards and checking/calibrating DC and AC ratio measuring instruments.

#### 4.2 Balancing (potential sharing) resistors

Connecting two separately constructed two-terminal pair resistors in parallel results in the following: -

Fig. 4.2.1 A pair of 2TP resistors in parallel

The aim is to be able to calculate the parallel combination accurately, in terms of the individual resistances: -

Ideally, for a parallel combination:

$$\frac{1}{R_r} = \frac{1}{R_r} + \frac{1}{R_r}$$

From the symmetry it is clear that there can be no advantage in having different resistances in the voltage sensing or current carrying connections (flip vertically and apply reductio ad absurdum). One can assume, therefore, that both voltage sensing connections for  $R_1$  have resistance  $R_{V1}$  and both current carrying connections have resistances  $R_{C1}$  and similarly for  $R_2$ .

The trick is to adjust the resistance in the current carrying connections so that no current flows in the voltage sensing resistances (i.e.  $V_1 = U_1 = U_2$  and  $V_2 = U_3 = U_4$ ).

$$U_3 = U_4 \qquad \Rightarrow V \frac{R_{C1}}{2R_{C1} + R_1} = V \frac{R_{C2}}{2R_{C2} + R_2}$$

Divide by V and take the reciprocal:  $\Rightarrow 2 + \frac{R_1}{R_{c1}} = 2 + \frac{R_2}{R_{c2}}$

From which one can derive the simple condition and define the parameter:  $\alpha = \frac{R_{C1}}{R_1} = \frac{R_{C2}}{R_2}$

From the symmetry the upper voltages must also be the same as the following confirms: -

$$U_1 = V \frac{R_{C1} + R_1}{2R_{C1} + R_1}$$

and  $U_2 = V \frac{R_{C2} + R_2}{2R_{C2} + R_2}$

In the first divide top and bottom by  $R_1$  and in the second by  $R_2$ : -

$$U_1 = V \frac{\alpha + 1}{2\alpha + 1}$$

and  $U_2 = V \frac{\alpha + 1}{2\alpha + 1}$  QED

With no current flowing through the voltage sensing connections one can confirm that the aim is achieved. According to Ohm's law: -

$$I_1 = \frac{U_1 - U_3}{R_1} = \frac{V_1 - V_2}{R_1} \qquad I_2 = \frac{U_2 - U_4}{R_2} = \frac{V_1 - V_2}{R_2} \qquad \text{and} \qquad I_1 + I_2 = I = \frac{V_1 - V_2}{R_1}$$

The net effective resistance is, therefore, exactly that for two basic resistors in parallel: -

$$\frac{1}{R_T} = \frac{I_1 + I_2}{V_1 - V_2} = \frac{1}{R_1} + \frac{1}{R_2}$$

One could, of course, add a third resistor, or as many as required, as long as the resistance in the current carrying pairs conforms to the requirement: -

$$\frac{R_{C1}}{R_1} = \frac{R_{C2}}{R_2} = \frac{R_{C3}}{R_3} = \dots = \frac{R_{CN}}{R_N}$$

From the symmetry it would also make sense if the resistances in the voltage sensing pairs were also matched: -

$$\frac{R_{V1}}{R_1} = \frac{R_{V2}}{R_2} = \frac{R_{V3}}{R_3} = \dots = \frac{R_{VN}}{R_N}$$

This is made clear by more detailed analysis, not included here as the algebra is a little tedious. For two resistors (see section 4.3.2 for a reference to the user manual): -

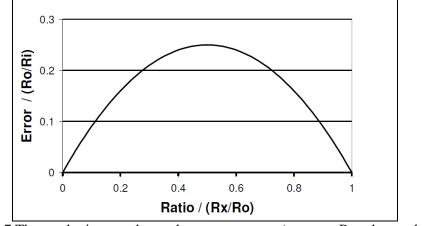

$$R_{T} = \frac{R_{1}R_{2}}{R_{1} + R_{2}} \left\{ 1 + \frac{R_{1}R_{2}}{R_{1} + R_{2}} \left( \frac{R_{V1}}{R_{1}} - \frac{R_{V2}}{R_{2}} \right) \left( \frac{R_{C1}}{R_{1}} - \frac{R_{C2}}{R_{2}} \right) \left( \frac{1}{R_{V1} + R_{V2}} \right) \right\}$$

It would seem a good idea, therefore, to match as closely as practicable both current carrying and voltage sensing connections. The most practical solution, however, given that resistance matching is only feasible to about  $1m\Omega$ , is to have very low resistance in the current connections (and switches) and larger, more closely matched resistances in the voltage sensing connections. Typical values are  $10m\Omega \pm 1m\Omega$  and  $1 - 10\Omega \pm 1m\Omega$  respectively. This is the basis of the White/Jones market leading resistance bridge calibrators.

## 4.3 Resistance bridge calibrators

There are two main types of resistor networks for bridge calibration: -

a). The Hamon type [1] was originally used to provide  $10\Omega$  and  $100\Omega$  transfer standards, calibrated against a  $1\Omega$  primary standard. It also provided limited means for checking the accuracy of ratio measuring instruments. The technique is now obsolete due to the development of the second type but is included for its ingenuity and for historical interest.

b). The White/Jones type [2] and [3] provides a much more practical means for checking the accuracy of ratio measuring instruments. Four accurate base resistors connected by a zero-Ohm junction provide a convenient method for generating an additional 31 calculable resistance values. When compared with a stable transfer standard resistor (e.g. a Wilkins) a full range of ratios can be measured and compared with calculated values. Unlike the Hamon type commercially available resistance bridge calibrators (RBC) also retain high accuracy at higher frequency (400Hz). Ratio accuracy can approach 10ppb especially with temperature control ( $\pm 0.01^{\circ}$ C).

The US National institute for Science and Technology (NIST) used the White/Jones type to compare five of the world's best selling resistance bridges with some very interesting results [4]: -

Fig 4.3.1 A report from NIST

4. Chojnacky, M. Kosior, J. Chaves-Santacruz, L. and Strouse, G.: "Performance assessment of thermometer resistance bridges". NIST Thermodynamic Metrology Group, Sensor Science Division

<sup>1.</sup> Hamon, B. V.: "A 1-100 $\Omega$  build-up resistor for the calibration of standard resistors". J. Sci. Instr. 31, 450-453 (Dec 1954).

<sup>2.</sup> US Patent 5,867,018 (Inventors: Rod White and Keith Jones): PCT/NZ95/00022

<sup>3.</sup> White, D.R. Jones, K. Williams, J.M. and Ramsey, I.E.: "A simple resistance network for calibrating resistance bridges". IEEE trans. on inst. and meas. Vol.46(5): pp.1068-1074. (1997)

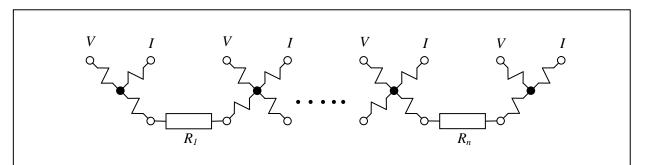

#### 4.3.1 The Hamon "build-up" network

The original Hamon network [1] consisted of eleven accurate  $10\Omega$  resistors permanently connected in series using type two zero-Ohm junctions. The two connections to each junction provide for two-terminal-pair measurement and comparison with a reference and with each other. Groups of resistors can then be connected in parallel or in series-parallel combinations, with suitable external matching resistors, to produce a wide range of resistor values (nominally  $1\Omega - 100\Omega$ ) and accurate ratios in the range 1:10 to 10:1. Hamon's analysis, later confirmed in more detail by Page [2] and Riley [3], showed that an accuracy of ±10ppb, or better, was "feasible". Although obsolete no monograph on high accuracy resistors would be complete without a mention of this ingenious design.

Fig. 4.3.1.1 A Hamon type network

Fig. 4.3.1.2 The Hamon network with external matching resistors

N.B. The original design employed pots of mercury to provide the very low resistance connections!

3. Riley, J. C.: "The accuracy of series and parallel connections of four terminal resistors." IEEE Trans. on Instr. & Meas. vol. IM-16. pp 258-268.

<sup>1.</sup> Hamon, B.V.: "A 1-100 $\Omega$  build-up resistor for the calibration of standard resistors". J. Sci. Instr. 31, 450-453 (Dec 1954).

<sup>2.</sup> Page, C. H.: "Errors in the Series-Parallel Build up of Four-Terminal Resistors" Journal of research of the National Bureau of Standards-C. Engineering and Instrumentation Vol. 69C, No.3, July-September 1965.

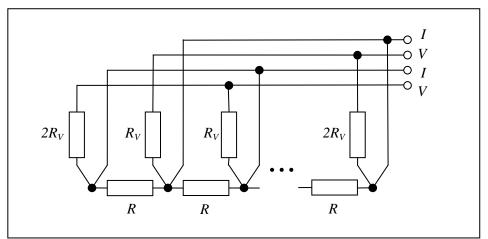

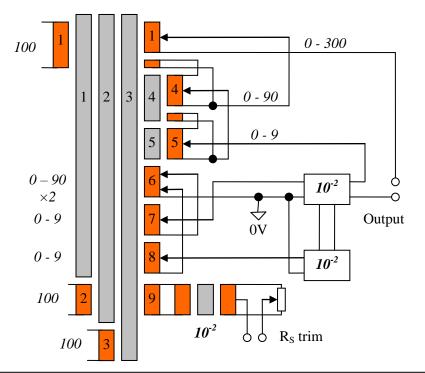

## 4.3.2 The White/Jones resistance bridge calibrator

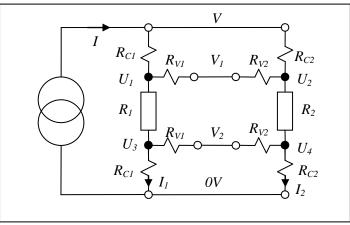

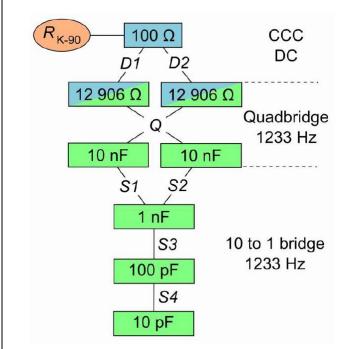

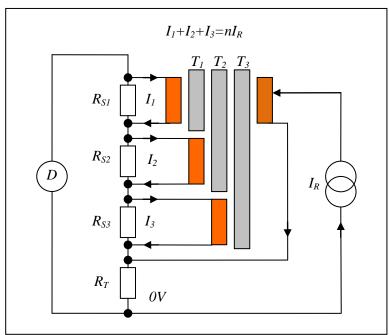

This ingenious design [1] supercedes the Hamon type and, when automated [2] and kept in a temperature controlled environment, provides a convenient method of checking resistance ratio measurement accuracy at the highest level. The following omits the small resistor symbols for clarity.

Fig 4.3.2.1 The White/Jones resistance bridge calibrator

(The USB controlled version is designed to be submerged in a temperature controlled oil bath)

Three models are available suitable for calibrating most commercially available resistance bridges, each with four very accurate resistors, four moderately accurate potential sharing resistors and a fully symmetric (type 3) zero-Ohm junction. The internal current carrying and switch contact resistances are kept very low. Each model is designed to provide a suitable range of ratios with transfer standard resistors of typically  $10\Omega$ ,  $25\Omega$  and  $100 \Omega$  respectively, depending on the measuring range of the instrument being calibrated. The potential sharing resistors are critical and are included below (resistance values in Ohms): -

| Model  | <b>R</b> <sub>1</sub> | $R_{P1}$ | $R_2$    | R <sub>P2</sub> | <b>R</b> <sub>3</sub> | $R_{P3}$ | $R_4$    | $R_{P4}$ |

|--------|-----------------------|----------|----------|-----------------|-----------------------|----------|----------|----------|

| RBC13  | 10.63652              | 2.635    | 6.26322  | 1.551           | 4.74705               | 1.176    | 4.06149  | 1.006    |

| RBC100 | 81.81935              | 2.645    | 48.17864 | 1.558           | 36.51578              | 1.180    | 31.24221 | 1.010    |

| RBC400 | 251.9874              | 3.177    | 147.9912 | 1.866           | 116.3731              | 1.467    | 40.4480  | 0.510    |

The values of the base resistors are chosen not only to provide an optimum range of ratios, when compared to a suitable transfer standard resistor, but also to exercise all nine digits of each decade, at least once, for detecting bridge malfunctions (e.g. a faulty relay).

The RBC User manual is available from Isothermal Technology Limited. <u>www.isotech.co.uk</u>

White, D.R., Edgar, H., McLennan, B.E., Saunders, P.: "Automation of the resistance bridge calibrator". AIP Conference Proceedings. Vol.1552, no. 8, pp 392-397 (2013).

Fig. 4.3.2.3 The internal connection scheme (the manual version has eight switches in total)

The four base resistors can be combined in various series, parallel and series-parallel combinations to provide an additional 31 resistor values which can be calculated (35 values in total). The range of values provides a relatively simple check on linearity of the instrument being tested to better than 100ppb. This is usually sufficient for most applications (e.g. resistance thermometry) as absolute values of resistance are not required.

Even more information (e.g. absolute ratio accuracy) can be gleaned if two or more (i.e. external to the bridge) transfer standard resistor values are available, providing more data points and permitting more complement and three resistor checks, subject to the range of the instrument: -

Complement check (swap resistors):

$$\frac{R_2}{R_1} \times \frac{R_1}{R_2} = 1$$

Three resistor check:

$$\frac{R_2}{R_1} \times \frac{R_1}{R_3} \times \frac{R_3}{R_2} = 1$$

## 5. Four-terminal-pair resistors

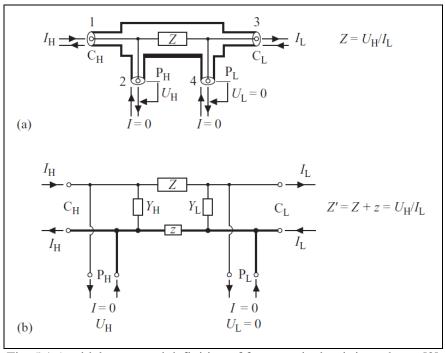

In much of the established literature the generally accepted definition of a four-terminal-pair resistor is a twoterminal-pair resistor with overall screen. This dates back many years. In one of the earliest papers Cutkosky, for example, regarded the screen connections as valid terminals of a four-terminal-pair device [1]. According to Awan et al "The result... is a four-terminal-pair definition, which is precise enough for all present practical applications and all values of impedances." [2].

Fig. 5.1 A widely accepted definition of four-terminal-pair impedance [2]

The result, over the years, has been complex bridge designs with earth loops and associated problems [3]. Fortunately there is a better way. The basic idea is to combine a two-terminal-pair resistor with a zero-Ohm junction (ZOJ type 1) plus an overall screen. The defining conditions remain the same: -

Fig. 5.2 The author's concept of a four-terminal-pair resistor

The measuring current is returned via the ZOJ in such a way that minimises the transmission of magnetic flux. Similarly, the voltage sensing connections are routed to minimise induced voltages due to stray magnetic flux. The screen is provided with a separate connection to local 0V and is insulated from the measuring terminals. Suitably insulated connectors (e.g. BNC co-axial) and insulating washers are readily available.

1. Cutkosky, R. D.: "Four-terminal-pair networks as precision admittance and impedance standards". Trans. IEEE Commun. Electron. 1964; **83**: pp19–22.

2. Awan et al. See footnote page 1.

3. Part 3, monograph 9: "Coaxial AC bridges".

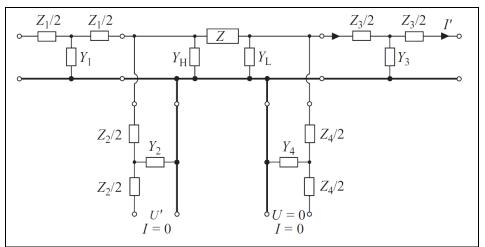

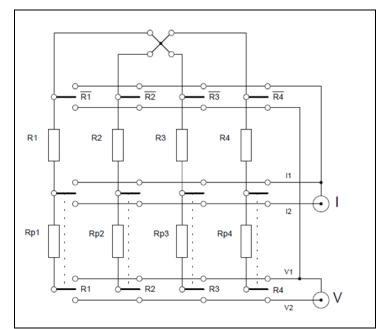

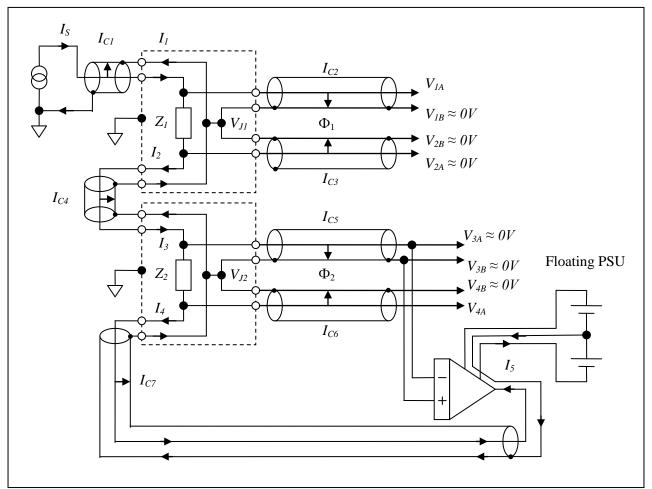

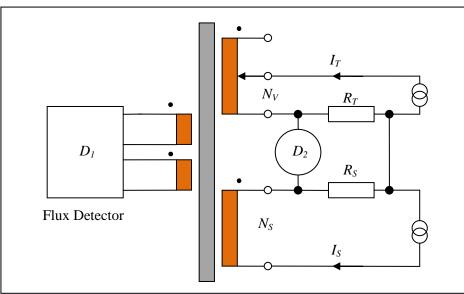

A typical measurement configuration is shown in fig. 5.3. The devices being measured are labelled as general impedances but can be resistive with small phase errors. The configuration ensures accurate equal and opposite currents and the minimal transmission of stray flux at the operating frequency without the need for high permeability toroidal chokes [1]: -

Fig. 5.3 Scheme for measuring the ratio of two four-terminal-pair resistors

Notes: -

1. The current source is shown with the usual symbol for simplicity. See fig. 5.5 for details.

2. The action of feedback of the high gain block is to ensure that the voltage across and, therefore, the currents through cable capacitances  $C_3$ ,  $C_4$ , and  $C_5$  are very small but may not be negligible. According to the definitions above the currents through  $Z_1$  and  $Z_2$  are, therefore: -

$$I_{Z1} = I_2 + I_{C3} \qquad \qquad I_{Z2} = I_2 - I_{C4} - I_{C5} \qquad \text{with} \qquad \left| I_{C3} \right|, \left| I_{C4} \right| \text{ and } \left| I_{C5} \right| << I_S \approx I_1 \approx I_2 \approx I_3 \approx I_4$$

3. Assume  $V_{1B} \neq V_{2B}$  and  $V_{3B} \neq V_{4B}$  because the zero-Ohm junctions may not be perfect and stray flux  $\Phi_1$  and  $\Phi_2$  between the cables may not be negligible. The relevant voltages are, therefore: -

$$V_{Z1} = (V_{1A} - V_{1B}) - (V_{2A} - V_{2B}) - V_{J1}$$

and  $V_{Z2} = (V_{3A} - V_{3B}) - (V_{4A} - V_{4B}) - V_{J2}$

Where  $V_{J1}$  and  $V_{J2}$  are the voltage generated at the (imperfect) zero-Ohm junctions.

*J. Res. NBS* – *C.* 1968; **72C**: 161–65

(A "Choke" is when the coax cable is passed through a toroidal core the required number of times)

<sup>1.</sup> Homan, D.N.: 'Applications of coaxial chokes to AC bridge circuits'.

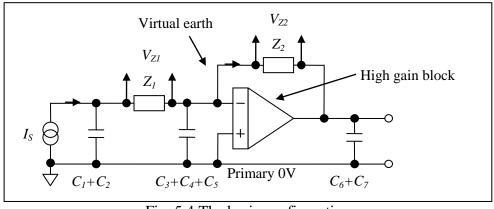

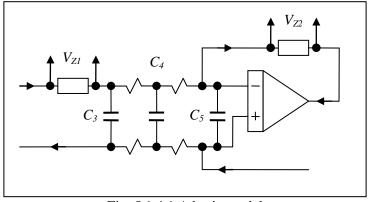

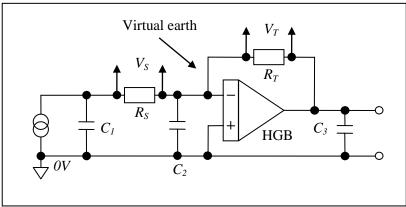

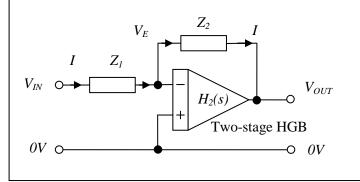

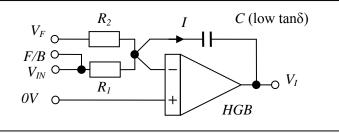

The circuit is basically an inverting amplifier [1] with a high gain block [2] with negligible input current providing an accurate virtual earth: -

Fig. 5.4 The basic configuration

Notes: -

1. There is only one connection to earth - no earth loops. This is usually at the current source for practical reasons. 2. The non-inverting input of the HGB can be regarded as the primary 0V reference point for the bridge. The virtual earth is maintained at this potential plus the DC offset and random noise of the HGB plus a very small carrier signal depending on the open loop gain.

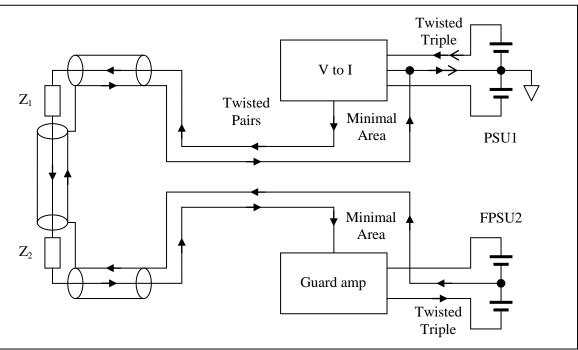

The current source and guard amp output stages are best constructed on the same PCB module with twisted triples for their (separate) power supplies and twisted pairs for the carrier signals. The principle can be best understood by considering the positive half cycle of the sine wave and following the route by which the current flows. Within the module the PCB tracks are routed to keep the area depicted to a minimum: -

Fig. 5.5 Physical layout and separate power supplies

The current source is usually a "Howland pump" type voltage to current converter which takes and returns a small but not negligible proportion of the total current back to the power supply hence the two pairs of arrows on PSU1.

- 1. Part 4, monograph 3: "High accuracy amplifiers, integrators and differentiators".

- 2. Part 4, monograph 1: "High gain blocks".

#### Analysis: -

According to Kirchhoff's law (conservation of charge) the currents flowing through the lumped impedances are, in the complex representation (phasors): -

$$I_{Z1} = I_2 + I_{C3}$$

$I_{Z2} = I_2 - I_{C4} - I_{C5}$  with  $|I_{C3}|, |I_{C4}| \text{ and } |I_{C5}| << |I_2| \approx I_s$

One can take the current  $I_s$  as the primary phase reference (i.e. a real number).

One can usually assume that any stray flux is sufficiently uniform so that the voltage induced between the conductors of a pair (coax or twisted) is negligible. According to Kirchhoff's laws, therefore: -

$(V_{1A} - V_{2A}) = V_{Z1} + V_I$  where  $V_I$  = the induced voltage due to  $\Phi_1$

$(V_{1B} - V_{2B}) = V_{J1} + V_I$  where  $V_J$  = the voltage error of the zero-Ohm junction.

$$\Rightarrow V_{Z1} = V_{1A} - V_{2A} - V_I = (V_{1A} - V_{1B}) - (V_{2A} - V_{2B}) - V_{J2}$$

Assume an ideal zero-Ohm junction though it would be wise to measure the voltage to be sure: -

$$V_{J1} = 0V \implies V_{Z1} = (V_{1A} - V_{1B}) - (V_{2A} - V_{2B})$$

Similarly for cables 5 and 6:

$$V_{Z2} = (V_{3A} - V_{3B}) - (V_{4A} - V_{4B})$$

The ratio of impedances is, therefore: -

$$\frac{Z_2}{Z_1} = \frac{V_{Z2}}{I_{Z2}} \times \frac{I_{Z1}}{V_{Z1}} = \frac{(V_{3A} - V_{3B}) - (V_{4A} - V_{4B})}{(V_{1A} - V_{1B}) - (V_{2A} - V_{2B})} \times \frac{I_2 + I_{C3}}{I_2 - (I_{C4} + I_{C5})}$$

$$\alpha = \frac{(V_{4B} - V_{4A})}{(V_{1A} - V_{1B})} \approx \frac{Z_2}{Z_2}$$

Define voltage ratio:

$$\alpha = \frac{(V_{4B} - V_{4A})}{(V_{1A} - V_{1B})} \approx \frac{Z_2}{Z_1}$$

This is very nearly the required ratio and needs to be measured very accurately.

Define voltage ratio:

$$\beta = \frac{(V_{3A} - V_{3B})}{(V_{1A} - V_{1B})} \approx \frac{(V_{3A} - V_{3B})}{V_{Z1}} << 1$$

The voltage difference  $(V_{3A} - V_{3B})$  is the error at the input of the high gain block and is very small.

Define voltage ratio:

$$\gamma = \frac{(V_{2A} - V_{2B})}{(V_{1A} - V_{1B})} \approx \frac{(V_{2A} - V_{2B})}{V_{Z1}} << 1$$

If one assumes an ideal HGB  $(V_{3A} - V_{3B} = 0V)$  the voltage difference  $(V_{2A} - V_{2B})$  is entirely due to the resistances in cable 4 and is also quite small.

Also, if the capacitive currents through cables 3, 4 and 5 are very small compared to the main current,  $I_2$ , then to a very good approximation: -

$$|I_{C3}|, |I_{C4}| \text{ and } |I_{C5}| \ll I_2 \qquad \Rightarrow \qquad \frac{I_2 + I_{C3}}{I_2 - (I_{C4} + I_{C5})} \approx 1 + \frac{I_{C3} + I_{C4} + I_{C5}}{I_2}$$

The ratio thus simplifies. To a very good approximation: -

$$\frac{Z_2}{Z_1} \approx \left(\frac{\alpha + \beta}{1 - \gamma}\right) \times \left(1 + \frac{I_{C3} + I_{C4} + I_{C5}}{I_2}\right)$$

A further approximation is possible: -

$$|\beta| \text{ and } |\gamma| \ll 1 \implies \frac{Z_2}{Z_1} \approx (\alpha(1+\gamma)+\beta) \times \left(1 + \frac{I_{C3} + I_{C4} + I_{C5}}{I_2}\right)$$

The voltage ratio  $\alpha$  must be measured very accurately as it is, by far, the major contributor. The much smaller voltage ratios  $\beta$  and  $\gamma$  can be measured with reduced accuracy.

In many cases, with fairly short lengths of cable, a two-stage high gain block and a low measuring frequency the correction factors are negligible and one can assume, with sufficient accuracy, the simple result: -

$$\frac{Z_2}{Z_1} \approx \alpha = \frac{V_{4B} - V_{4A}}{V_{1A} - V_{1B}}$$

#### **5.1 Example calculations**

This type of arrangement can be used for measuring the ratio of relatively high value resistors, usually for comparing transfer standards. I shall assume that  $Z_1$  and  $Z_2$  are  $10k\Omega$  transfer standard resistors with small phase errors. The current source is a generous  $100\mu$ A (pk-pk) at 75Hz ( $\omega = 471$ radians/s) resulting in voltage drops across the resistors of  $V_{Z1}$  and  $V_{Z2} \approx 1$ Vpk-pk.

The power dissipation is 0.1mW and, with a little care taken in the thermal design, self heating is not an issue.

## **5.1.1** Cable phase and magnitude errors

A reasonable assumption for the cables is 1m long with  $\approx 0.1\Omega$  series resistance (both conductors) and 100pF of parallel capacitance. At low frequency each centimetre of cable can be approximated as a low pass filter with  $\approx 1 \text{m}\Omega$  resistance and 1pF capacitance with a transfer function, for *N*cm, in the complex representation ( $s = j\omega$ ):

$$T_N(s) \approx \frac{1}{(1+\tau s)^N} \approx 1 - N\tau s \text{ with } \tau = RC < 1m\Omega \times 1pF \approx 10^{-15} s$$

The total phase error (quadrature) for each 1m of cable is, therefore:  $N\tau\omega < 4.71 \times 10^{-11}$  radians and negligible. The real part (in-phase) is second order with respect to frequency and even smaller.

Also, electromagnetic signals travel along most types of cable at about two thirds the speed of light ( $\approx 2 \times 10^8 m s^{-1}$ ). which, at 100Hz (period 10ms) represents a phase shift of  $5 \times 10^{-7}$  radians per metre of cable. **Time delays are negligible.**

Similarly, the loss factor ("tanő") of the insulating dielectric of reasonably good quality cable is very small (typically  $<10^{-3}$  rad) and represents small phase errors in the currents  $I_{CI} - I_{C7}$ . Cable phase and magnitude errors are truly negligible.

#### 5.1.2 Zero-Ohm junction errors

Type 1 zero-Ohm junctions are easily constructed and checked and, if necessary, adjusted to  $<10n\Omega$  (with 1A measuring current the output is <10nV). At an operating current of 100µA the error voltage is then negligible.

#### 5.1.3 HGB error voltage

The recommended HGB is a two-stage (type 1) for which the main error voltage is in-phase [1]. An open loop gain of  $10^9$  is readily achieved at 75Hz. With an output voltage of 1V (pk-pk) the input error voltage is less than 1nV (pk-pk). The correction factor  $\beta$  is then very small and usually negligible: -

The transfer function of the HGB is defined by:

$$H_2(s) = \frac{V_{4A}}{V_{3B} - V_{3A}}$$

For an ideal inverting configuration:

$$V_{4A} = -\frac{Z_2}{Z_1} V_{1A}$$

$$Z_2 \approx Z_1 \text{ and } V_{1B} \approx 0V \implies \beta = \frac{V_{3A} - V_{3B}}{V_{1A} - V_{1B}} \approx \frac{V_{3B} - V_{3A}}{V_{4A}} \left(\frac{Z_2}{Z_1}\right) \approx \frac{1}{H_2(s)} \left(\frac{Z_2}{Z_1}\right) < 1ppb$$

1. Part 4, monograph 1: "High gain blocks".

If one assumes negligible resistances in cable 4 the error voltage results in negligible currents through the capacitances of cables 3, 4 and 5: -

$$I_{2} \approx I_{4} \approx -\frac{V_{4B}}{Z_{2}} \quad \text{and} \quad I_{C3} + I_{C4} + I_{C5} = (V_{3A} - V_{3B})s(C_{3} + C_{4} + C_{5})$$

$$\Rightarrow \quad \frac{I_{C3} + I_{C4} + I_{C5}}{I_{2}} = \frac{j\omega(C_{3} + C_{4} + C_{5})Z_{2}}{H_{2}(s)} \quad (\text{quadrature})$$

With a total cable capacitance of 300pF at 75Hz the error term is negligible ( $Z_2 = 10k\Omega$ ): -

$$\left|\frac{I_{C3} + I_{C4} + I_{C5}}{I_2}\right| < 1.4 \times 10^{-12}$$

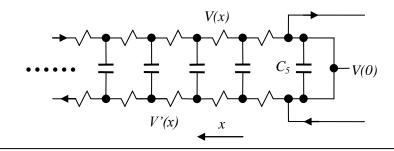

#### 5.1.4 Resistance in cable 4

The measuring current flows through cable 4 creating a small voltage gradient and currents through  $C_3$  and distributed  $C_4$ . A basic model consists of half the conductor resistance either side of the actual capacitance of cable 4. Note that the measuring current does not flow through any part of cables 3 or 5: -

Fig. 5.1.4.1 A basic model

This is worth checking as the distribution of resistance and capacitance is continuous. If one assumes an ideal HGB: -

Fig. 5.1.4.2 A gradient model for cable 4

Define parameters: -

L = Length of cable 4 in metres

$\rho$  = Resistance per unit length of the inner conductor ( $\Omega m^{-1}$ )

- $\rho'$  = Resistance per unit length of the outer conductor ( $\Omega m^{-1}$ )

- $\sigma$  = Capacitance per unit length (Fm<sup>-1</sup>)

$\omega$  = Operating frequency (rads<sup>-1</sup>)

x = Distance from the HGB end in metres

According to Ohm's law the voltages along the inner and outer conductors of cable 4 vary according to: -

$$V(x) = V(0) + I_2 \rho x$$

and  $V'(x) \approx V(0) - (I_2 + I_{C6} + I_{C7}) \rho' x$  respectively

The currents caused by the capacitance of cables 6 and 7 are very small compared to the measuring current so that the difference voltage is, to a sufficiently good approximation: -

$$\left|I_{C6} + I_{C7}\right| \ll I_2 \implies V - V' \approx I_2(\rho + \rho')x$$

The capacitive current over the infinitesimal distance dx is:

$$dI_{C4} = I_2(\rho + \rho')s\sigma x dx$$

If one assumes that  $\rho$  and  $\rho'$  are constant (uniform resistance along the cable), being careful to employ good quality, low contact resistance connectors, the integral is simple: -

$$\frac{I_{C4}}{I_2} \approx \left(\rho + \rho'\right) s \sigma \frac{L^2}{2} = \frac{R + R'}{2} s C_4$$

Where R + R' = total resistance (inner and outer) of cable 4, confirming the basic model of fig. 5.1.4.1. The voltage across cable 3 also results in a current: -

$$\frac{I_{C3}}{I_2} = (R+R')sC_3$$

$$\frac{I_{C5}}{I_2} = 0$$

$I_2$

The voltage across cable 5 is zero so that:

The correction factor is, therefore:

$$\frac{I_{C3} + I_{C4} + I_{C5}}{I_2} = \left(R + R'\right) s \left(C_3 + \frac{C_4}{2}\right)$$

With each cable 1m long (100pF) and a total resistance of  $0.1\Omega$  (inner plus outer) the correction factor is: -

$$\frac{I_{C3} + I_{C4} + I_{C5}}{I_2} = j \times 0.1 \times 471 \times 150 \times 10^{-12} \approx j7.1ppb \quad (\text{quadrature})$$

This is easily rejected with a suitable quadrature null balance servo.

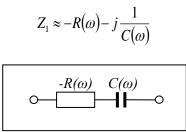

# 5.2 Calculable resistors

In recent years there has been a revival of interest in the link between the Farad (the SI unit of capacitance) and the Ohm (the SI unit of resistance) via a quadrature bridge [1]. The traceability chain is nicely summarised in a diagram: -

Fig. 5.2.1 Links in the traceability chain from Ohm to Farad (courtesy METAS [3])

The best QHR standards and cryogenic current comparators (CCC) employ alternating DC or very low frequency AC (<1Hz) for comparing resistors. The reasons include: -

a). Power dissipation within the cryostat and heat conduction down the connections must be very low. One consequence is long and very thin coaxial connections with significant series resistance and parallel capacitance. Some of the capacitive current inevitably flows through part of the series resistance resulting in heat dissipation and measurement errors which increase with frequency.

b). The very high magnetic field employed results in a force on any current carrying conductors. The result is unwanted vibration which manifests as increased series inductance as well as more heat dissipation.

c). Stray capacitance within and from the QHR to its surroundings also result in errors which increase with frequency [2].

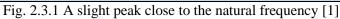

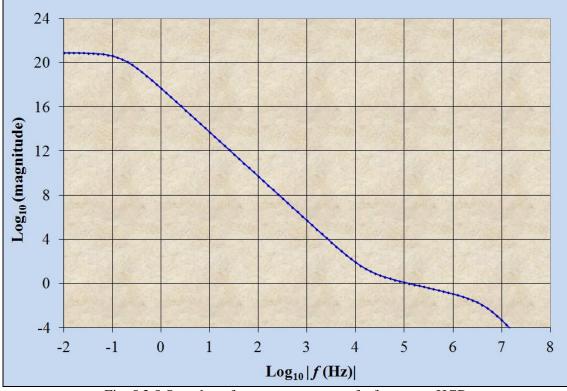

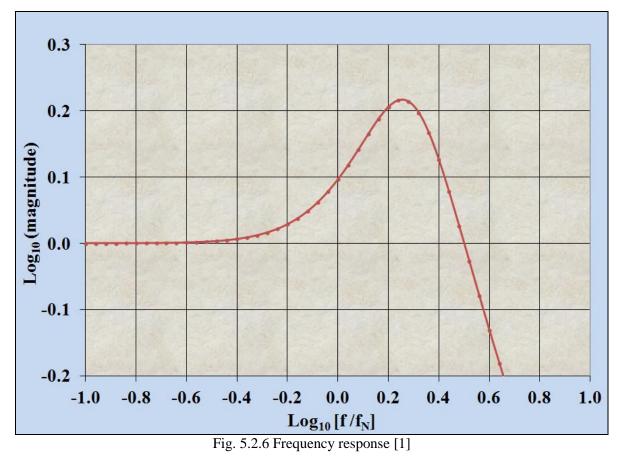

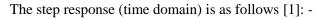

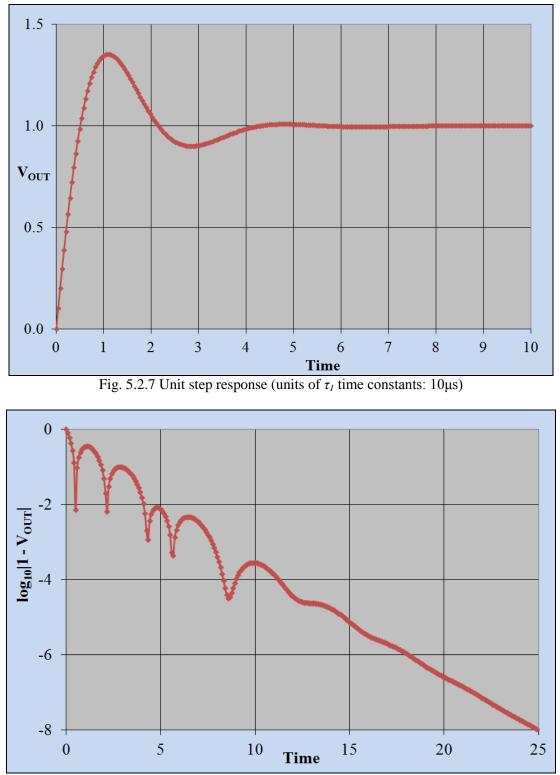

The optimum frequency for measuring capacitance, on the other hand, is around 1-10 kHz. There is a need, therefore, for a type of transfer standard resistor with calculable magnitude and phase as a function of frequency (typically up to 10 kHz), based on a measured DC value and ("a priori") fundamental principles.

The AC characteristics of a more robust (portable) type of resistor (e.g. Vishay) can then be established, with a coaxial AC bridge, which is then passed around various NMIs for comparing with capacitors using a "quadrature" bridge [1].

For a comprehensive review see [3].

1. Part 3, monograph 10: "A quadrature bridge"

Ahlers F. J., Jeanneret B., Överney F., Schurr J. and Wood B. M.: "Compendium for precise ac measurements of the quantum Hall resistance." Metrologia (Oct 2009). DOI: 10.1088/0026-1394/46/5/R01

Schurr, J. et al: "Final Report of the Supplementary Comparison EURAMET.EM-S31: Comparison of capacitance and capacitance ratio (May 2017). There are two main types of (a priori) calculable resistor. Both rely on relatively simple geometry so that the impedance can be modelled analytically (in terms of "lumped" components – resistance, inductance and stray capacitance) as well as calculated using finite element analysis:-

a) The coaxial or "Haddad" type [1].

b) The bifilar, quadrifilar and octofilar or "Gibbings" type [2].

Both are sensitive to shock and vibration and require very accurate temperature control. They must be moved, very gently, between the QHR/CCC and adjacent higher frequency apparatus and back again whilst maintaining a constant temperature. The more robust transfer standard resistors and/or capacitors can then be transported (usually by hand) to other calibration labs.

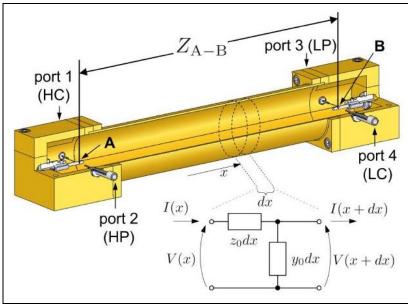

Fig. 5.2.2 A coaxial type calculable resistor (courtesy METAS)

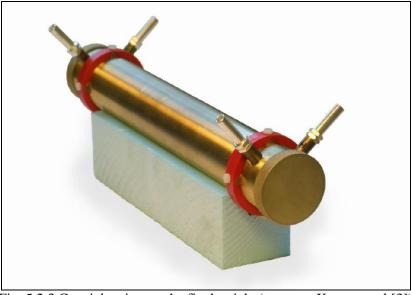

Fig. 5.2.3 Coaxial resistor – the final article (courtesy Kucera et al [3])

1. Haddad R. J.: "A resistor calculable from DC to  $\omega = 10^5$  rad/s," Sch. Eng. Appl. Sci., George Washington Univ., M. S. Thesis (Apr. 1969) 2. Gibbings, D. L. H.: "A design for resistors of calculable ac/dc resistance ratio" Proc. IEE vol. 110 pp. 335–347 (1963) 3. Kucera, J., Vollmer, E. and Schurr, J: "Precision Haddad-type Calculable Resistors". Presentation to CPEM/PTB 2008.

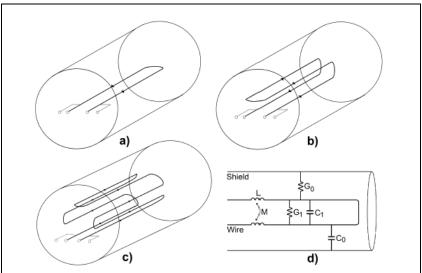

Fig. 5.2.4 Calculable resistors - basic construction and model (courtesy Pacheco-Estrada et al [1]): -

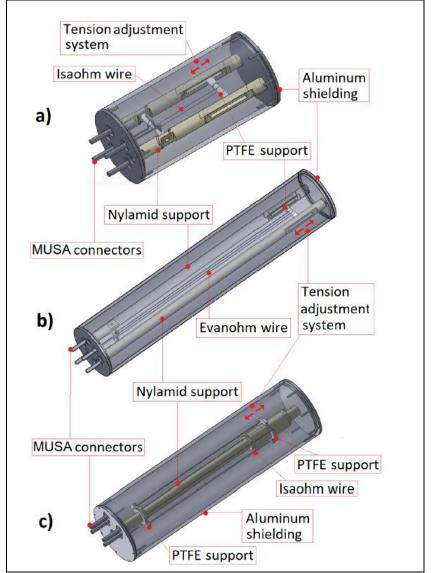

Fig. 5.2.5 Calculable resistors - construction details (courtesy Pacheco-Estrada et al [1]): -

1. Pacheco-Estrada, A. H. et al: "A Simple Methodology to Develop Bifilar, Quadrifilar and Octofilar Calculable Resistors". Appl. Sci. **2020**, 10, 1595.

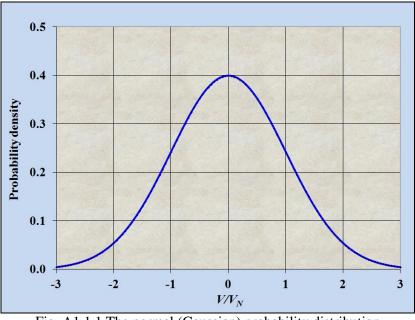

#### 6. Johnson Noise

One of the main disadvantages of resistors is that they generate random noise. The free electrons within the resistor behave much like a gas - flying about in random directions with a normal (i.e. Gaussian) energy distribution. With a low noise amplifier it is possible to measure a small random voltage at the terminals. The open circuit noise voltage (RMS) is: -

$$V_{IN} = \sqrt{4kTBR}$$

Where: -

$k = 1.38 \times 10^{-23} JK^{-1}$  is Boltzmann's constant T = Absolute temperature (K) B = Bandwidth in Hz R = Resistance in Ohms

Similarly the closed circuit noise current (RMS) is:

$$I_{JN} = \sqrt{\frac{4kTB}{R}}$$

The "noise power" is a useful concept: -

$$P_{JN} = V_{JN}I_{JN} = 4kTB$$

It is shown elsewhere [1] that the noise power is four times the heat energy which would flow down the conductors from a warm source resistor to a matching cold resistor.

Similarly, best noise performance is obtained when the first stage amplifier is matched to the source resistance [1]. This occurs when the noise resistance (noise voltage divided by noise current) of the amplifier input stage is equal to the source resistance. Bipolar transistors are best matched to resistances between  $100\Omega$  and  $10k\Omega$  [2]. Matching to lower source resistance can be achieved with a suitable transformer [3]. Matching to higher value resistance is typically improved by using a JFET transistor input stage ( $100k\Omega - 10M\Omega$ ) [4].

- 2. Part 5, monograph 2: "Low noise BJT pre-amps"

- 3. Part 3, monograph 5: "Noise matching transformers"

- 4. Part 5, monograph 3: "Low noise JFET pre-amps"

<sup>1.</sup> Part 5, monograph 1: "Null detectors - the basics". See appendix A1.1 and A1.3

# 7. Picture gallery

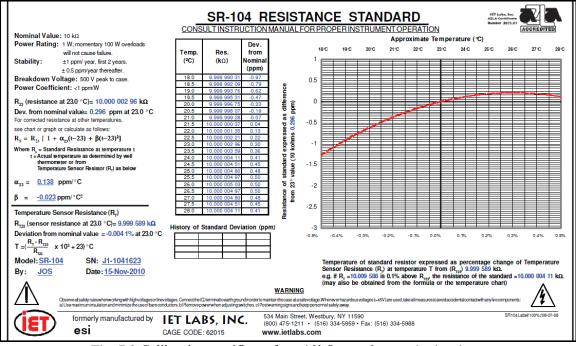

Fig. 7.1 A transportable  $10k\Omega$  transfer standard resistor (courtesy IET Labs inc.)

An alternative to accurate temperature control is either by measuring the temperature of the oil bath with a separate thermometer (thermometer well provided) or by measuring the incorporated resistance thermometer (nominally  $10k\Omega$ ) with a dedicated channel on a scanner. The calibration certificate provides the known dependence: -

Fig. 7.2 Calibration certificate for a  $10k\Omega$  transfer standard resistor

# **High accuracy single capacitors**

## 1. Introduction

High accuracy single capacitors are used as calibration transfer standards and convenient reference devices for capacitive sensors (e.g. variable gap, humidity and strain gauges). For some years a calculable capacitor was also a serious contender as a primary standard for the Ohm [1 and 2]. Attempts have also been made to construct capacitors with a fused quartz dielectric [3] but the most common types use air as a dielectric. The capacitance varies slightly with temperature, pressure and humidity. Temperature sensitivity can be mitigated by choosing materials and relative dimensions whereby the expansion coefficient is self-compensating, at least over normal lab temperatures and with stable temperature control. An empirical formula can be used to compensate for variations in atmospheric pressure and humidity [4]. For the very highest accuracy the capacitor can be flushed through with dry air and then sealed.

According to Marina Santo Zarnik and Darko Belavic: "The permittivity of the air as a function of the relative humidity can be calculated from the empirical relation [4]: -

$$\varepsilon_{air} = \varepsilon_0 \cdot \left[ 1 + \frac{211}{T} \cdot \left( P + \frac{48 \cdot P_S}{T} \cdot RH \right) \cdot 10^{-6} \right]$$

where  $\varepsilon_0$  is the permittivity of vacuum, *T* is the absolute temperature (K), RH is the relative humidity (%), *P* (mm Hg) is the pressure of the air, and  $P_s$  (mm Hg) is the pressure of saturated water vapour at the temperature *T*".

Fig. 1.1 A 1pF reference capacitor (picture courtesy ASL Ltd)

2. Thomson, A. M. 1958.: "The precise measurement of small capacitances."

IRE Trans. Instrum. I7 245-53.

- 3. Cutkosky, R. D. and Lee, L. H.: "Improved ten-picofarad fused silica dielectric capacitor." NBS J. Res., vol 69C, pp 173 179, July Sept 1965.

- 4. Santo Zarnik, M. and Belavic, D.: "An Experimental and Numerical Study of the Humidity Effect on the Stability of a Capacitive Ceramic Pressure Sensor". Radioengineering, Vol. 21, No. 1, April 2012 201. http://www.radioeng.cz/fulltexts/2012/12 01 0201 0206.pdf

<sup>1.</sup> Raynor, G. H.: "NPL Calculable Capacitor." IEEE Trans. Instrum. Meas. Vol IM-21. Pp 361 – 365, 1972.

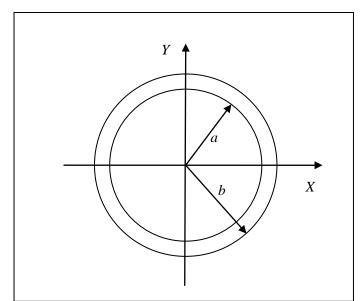

# 2. Transfer standard air capacitors

Transfer standard air capacitors are usually fabricated as concentric cylinders, machined to high precision and mounted on ceramic insulators inside a screened metal enclosure.

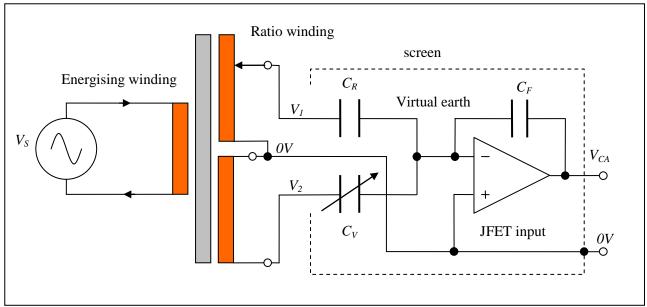

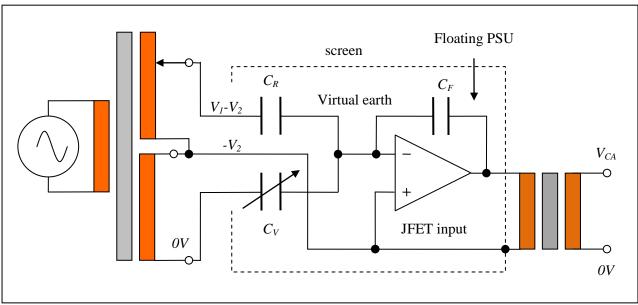

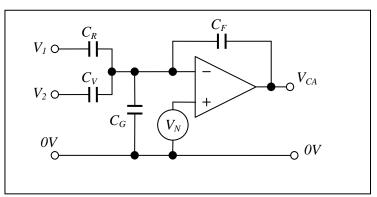

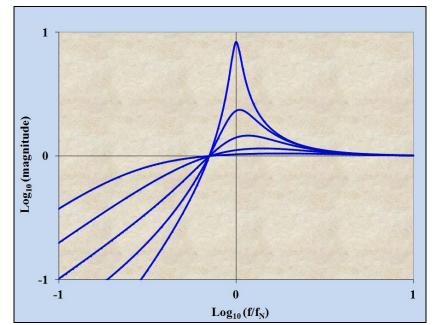

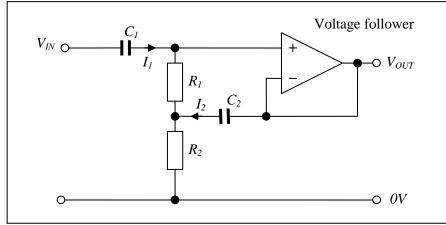

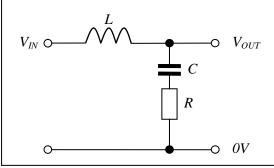

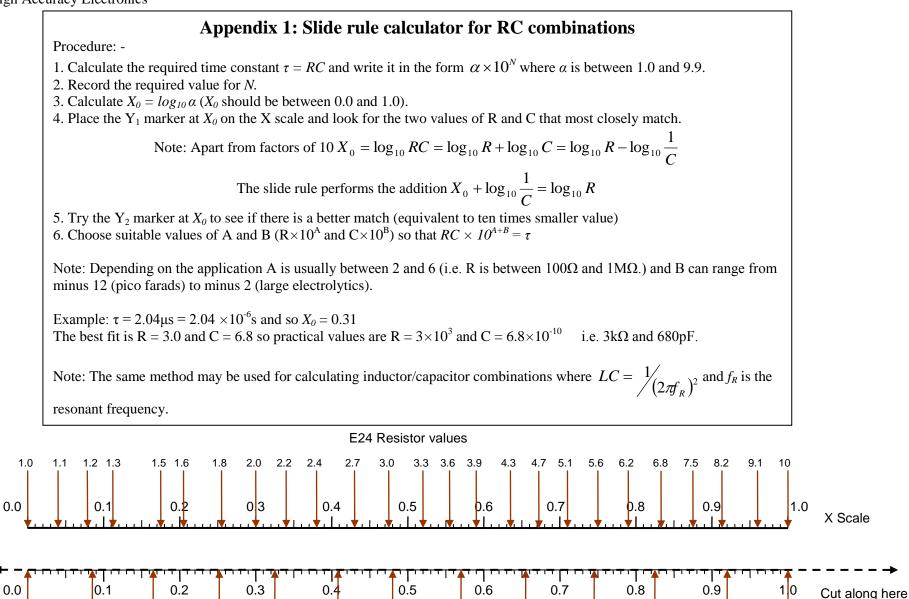

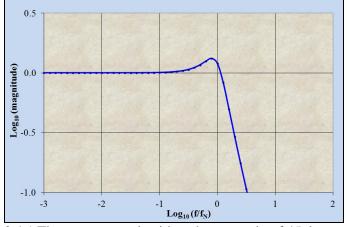

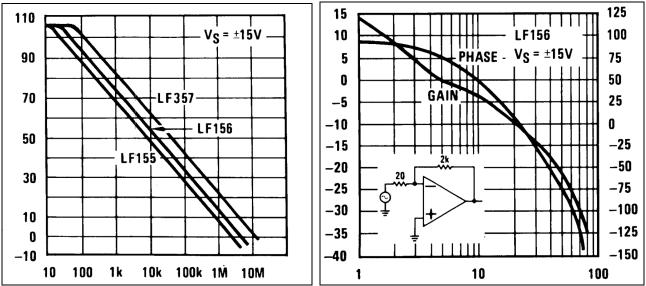

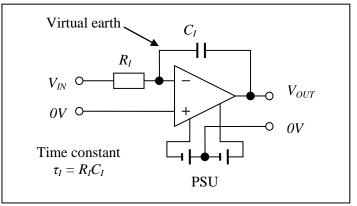

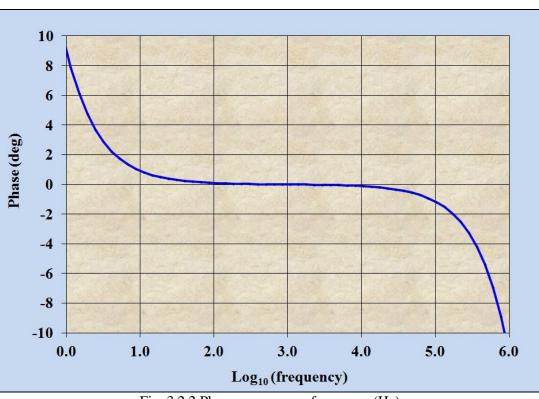

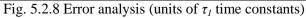

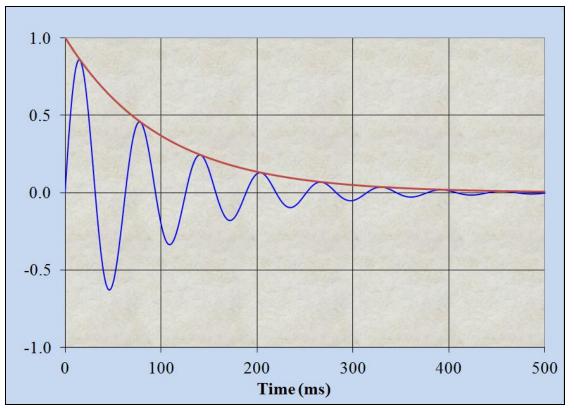

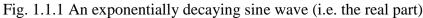

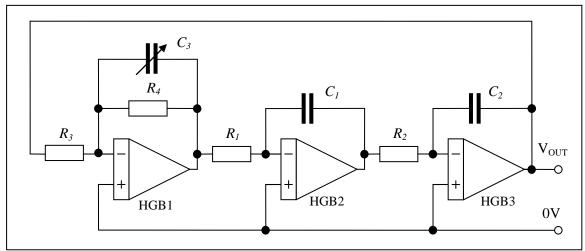

Fig. 2.1 A 10pF transfer standard capacitor (picture courtesy ASL Ltd)