What is this Nanovolt Challenge?

What is this Nanovolt Challenge?Welcome to this friendly competition dedicated to building some nanovolt-grade hardware and analog designs! This public challenge dedicated for making your own open-source DC Voltage measurement device. Main audience is the electronic design engineers and metrology scientists, who have practical interests in performing very low level DC Voltage signal measurements (microvolt level and below).

Main goal of this contest is to show practical benefits of proposed nanovolt-capable design, not just theoretical possibility of such. There are many new ideas for low-level DC voltage measurements available with modern electronics and advance in digital and analog circuit designs, but very few are actually publicly discussed or demonstrated. This contest main goal is to promote such ideas and show openly what can be achieved in practical accomplished device.

Challenge terms and rules

Challenge terms and rulesFor international metrology community benefits it was decided that each project must comply with next conditions:

* Each submission entry must be based on actual physical design prototype and include design, measurement results and proof of operation.

* Submissions must be completed in

256 days term between

September 2, 2021 23:59 EST and

May 16, 2022 23:59 EST.

* All design information, including schematics, PCB files (not only Gerbers), libraries, simulation files and source code/firmware files must be publicly available under free to reuse license.

* Wiki or work log write-up about the project (at least 2000 words) with permission to publish it on xDevs.com site.

* There is no budget or component selection limit, as far as previous conditions about public design information is met.

* All designs must come with some sort of verification and performance results data. Noise, gain accuracy, thermal stability (+18 to +28 °C) and linearity parameters data is expected.

* Must not violate any commercial IP or 3rd-party license(s) (e.g. reverse-engineered commercial nano-voltmeter is not OK).

* All submissions must be written in English language.

Bonus point – if you were already working on nanovolt-related project before September 2, 2021, you can reuse any existing hardware, software or firmware and knowledge acquired, given that it should be published within submission entry and released for public as result.

Criteria for project relevance for acceptanceProposed design must include hardware and software/firmware related to functionality of the unit. Additional calibration and used testing fixtures information is not required but very welcome. To focus design around somewhat common goal each of the nanovolt device entry should be able to perform next functionality to be accepted:

* Have local onboard power regulation. Single common DC (+9 to +24 VDC) or 110/220VAC mains input jack is expected.

* Provide DC Voltage measurement ranges ±100 µV or below and include ±1V and ±10VDC range.

* Have at least two user-accessible input channels for signal to be measured.

* Have low-thermal connection interface to minimize thermal EMF parasitic errors.

* Provide at least 5½-digit resolution for each reading.

* Ability to digitize input DC signal with resolution at least 10 nV and noise better than 30 nV peak to peak over at least 0.1-10 Hz bandwidth.

* Have autozero functionality to correct for static offsets.

* Have galvanic isolated analog front end, with isolation resistance to earth/chassis better than 10 GΩ.

* Device should have ADC (any type) integrated.

* Have good long-term stability and use ovenized DC voltage reference (LM399, LTZ1000 or LTFLU with oven).

* Provide RJ45 Ethernet and/or IEEE-488 GPIB interface for communications with external world / external equipment.

* 40W total input power budget (friendly to battery operation for sensitive experiments)

* Device should be fully operational as standalone device (e.g. no debuggers or external equipment attached to make it work).

Everything else is up to designers, no other limitations or restrictions. References with voodoo-slots, multi-layer PCBs, fancy OLED displays, Raspberry Pi controllers, gold-plated Titanium enclosures – all is welcome.

Compensation for winning projectSince reaching goals of the project are not easy nor simple additional motivation is provided for the best design award.

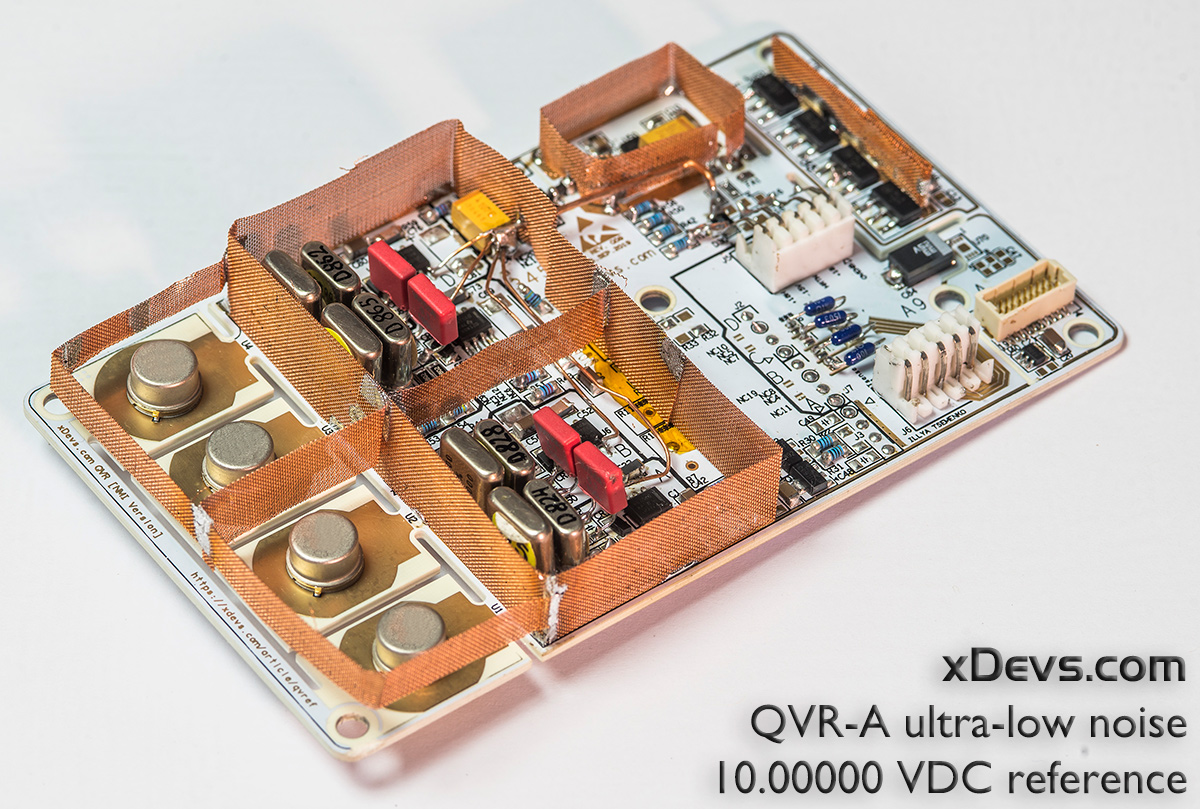

* Special version of xDevs.com QVR-A module with four of brand new Analog Devices ADR1000 ultra-low noise references.

* Calibration of QVR-A module on Josephson Junction Voltage Quantum Standard (once) with uncertainty below 0.1 ppm.

Reference will be packaged in custom rugged aluminum enclosure with low-thermal connectors and protected in hard-case shipping container.

Shipping cost of the QVR-A and JVS calibration will be covered by xDevs.com. Projects will be judged and carefully reviewed after challenge reach the deadline cutout. Final results and ranking will be provided on this page no later than June 16, 2022 23:59 EST. Reference and calibration will be shipped to winner no later than July 31, 2022.

Additional items and prizes might be added in future.

Full details about this challenge contest provided here. Instructions for project submissions are there as well.

Discussion and feedback also can be done in this thread.