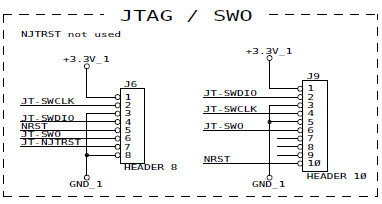

Currently, on my target I have these two connectors

(actually on J9, 3,5,7,9 are all GND)

J6 connects to the 20-way big connector on the STLINK V2 / STLINK V3 debuggers. This works. NJTRST isn't connected. I originally did a lot of googling on this and found a vast number of people asking the same question, with no real answers

J9 is the "standard ARM debug" pinout documented by various debugger tool makers e.g. Keil, and is supported by STLINK V3 via its CN1 connector and the 14-way to 10-way cable they provide. This doesn't have NJTRST.

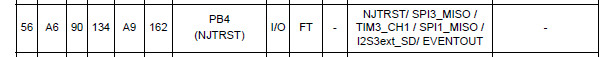

I sort of understand this ST world isn't actually JTAG but an ST-special single wire debugging thingy. So maybe this is why NJTRST is not used. But it takes up PB4 which could otherwise be useful

Currently I have a 10k pullup on PB4, just in case

The data sheet is silent on PB4 mode. The ref manual describes how it can be used for stuff according to whether Jtag is configured, and it mentions an internal pullup but doesn't say whether this pullup is always present.