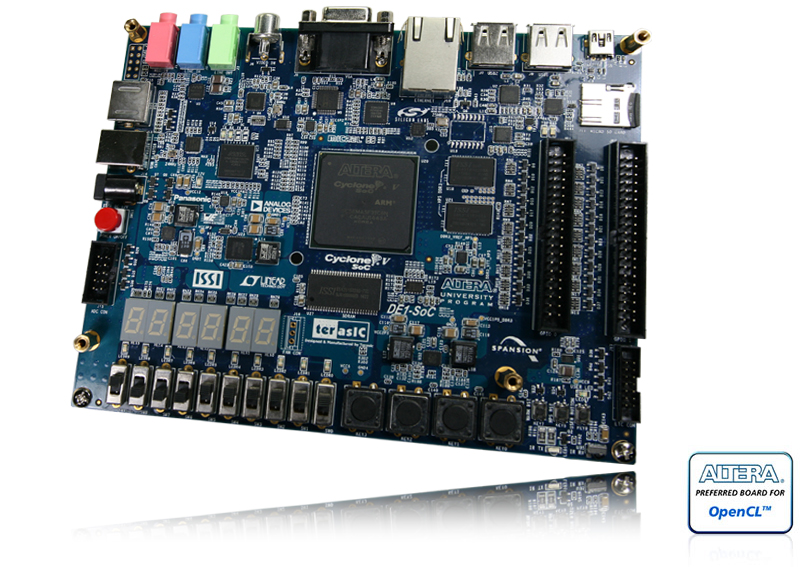

Hope you can share my excitement, as I should be getting Digikey box tomorrow, with brand new Terasic DE1-SoC with that fancy ALTERA (or should I say now Intel?) FPGA+ARM Cyclone V.

I have and used few older Terasic boards before, like Cyclone II DK20 and DE0-nano (MAX2 2210), so choice for Cyclone V was straightforward.

My main intention for this is to have it run linux on ARM side, try to get linux-gpib working on it and use FPGA to talk with various analog stuff.

Linear DAC board is coming same box as well, and I'll try generating some precision AC with help of it.

Never used these new ARM&FPGAs chips before, so if you have something to say about 'em or interesting projects - feel free to tell.

Eventually I'll have ADCs and some front-ends made for it to make it into some usable lab tool. Perhaps with an LVDS panel as well.