Some news and results.

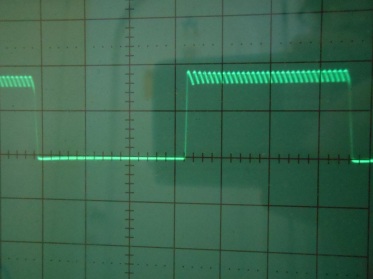

This is the real circuit, with BUZ70 with no compensation, Val = 8V for opamp and MOS:

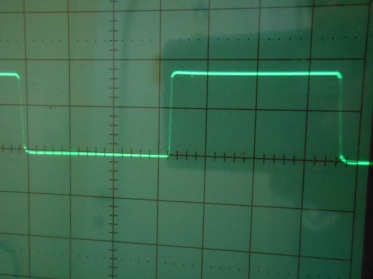

and inserting C=10nF, R=100ohm became:

The circuit was made on a 2layer PCB:

The blue resistor and the cap are the compensations. The others are pulldown on opamp input and the sense resistor, which is 4.7ohm. The MOSFET is BUZ70.

I don't know why, but using 1000ohm resistor and 1nF will oscillate even more.Now, with a new circuit which uses the "fatter" MOSFET IRLI630, uses also a resistor of 0.47ohm because the input also is 10 times lower. I don't have screens of the oscillations, but here what happens:

with the compensation like with the BUZ70, does not work, it is very noisy at 12V and oscillate up to saturation under 12V.

Inserting a 100uF electrolytic cap on Val, works well at 12V, became noisy at 5V and at 3.3V there is a ringing even greater than the one in picture before, at around 100kHz.

Then I tried with pole-zero compensation at 100kHz (between + and - of opamp), changes only a bit. Increasing with dominant pole by putting R=200ohm and not using zero-pole, therefore around 80MHz, it does not change anything. Using both solutions make the condition worst. I know, the inductance could be present on voltage lines, and the power supply is a PC's PSU, noisy, but my control loop is somewhat still unstable.

The requirement I'm looking for is high speed (between 150 and 200kHz at least) and a current precision which can be inside 5%.

Here in this forum are supported also projects, if I can be helped to going out from this stuck condition, I can start a new topic about it, and provide updates, if it worth. It is a 4 colour lamp, driven with 4 PWM channels from a micro, which I'd like to make in switching version (I am currently working on it) and a linear one, which could be used to modulate signals (here why the precision and frequency initial requirements).