It seems I have postet the IK72 before I startet to post the parts here in the EEVblog-Forum. Now that I have a second (different) IK72 lets talk about both.

The IK72 is the first monolithic integrated analogue circuit developed in the GDR. The development took place in the R&D department of the Halbleiterwerk Frankfurt Oder (HFO) in Stahnsdorf. The first components were available in 1972. The IK72 represents a differential amplifier including a current sink that can be used for various circuits. Compared to a discrete differential amplifier, an integrated differential amplifier has the great advantage that the transistors have very similar characteristics and also operate at relatively the same temperature levels.

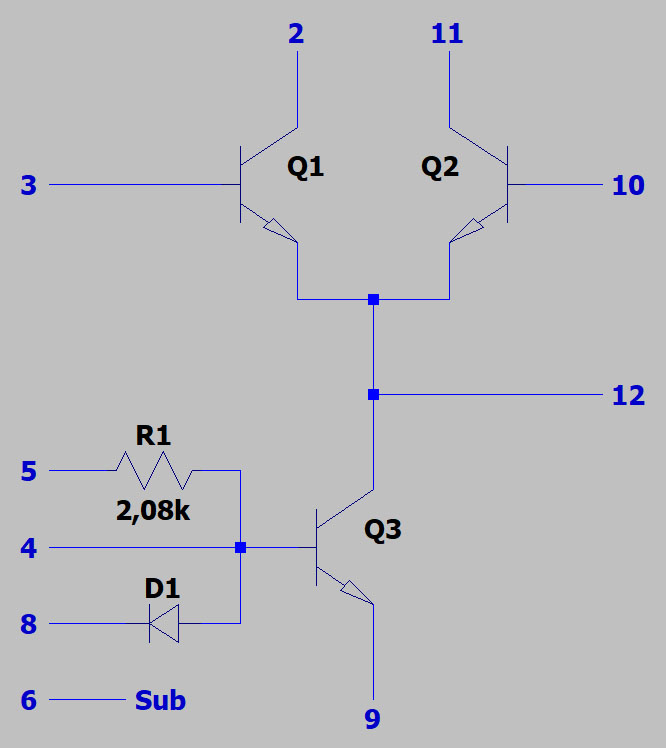

Very little is known about the IK72. The information available online so far was limited to a circuit example from an RFE magazine (1974/18). According to this, the IK72 contains a differential amplifier consisting of two transistors with a third, common transistor at the emitters. However, the article also points out in this circuit diagram that "only the wired parts are shown".

The model seen here is marked with a paper banderole and comes from a developer who should develop a PLL circuit in 1975. It is therefore almost certainly a real IK72.

The full designation is IK72-13 0109.

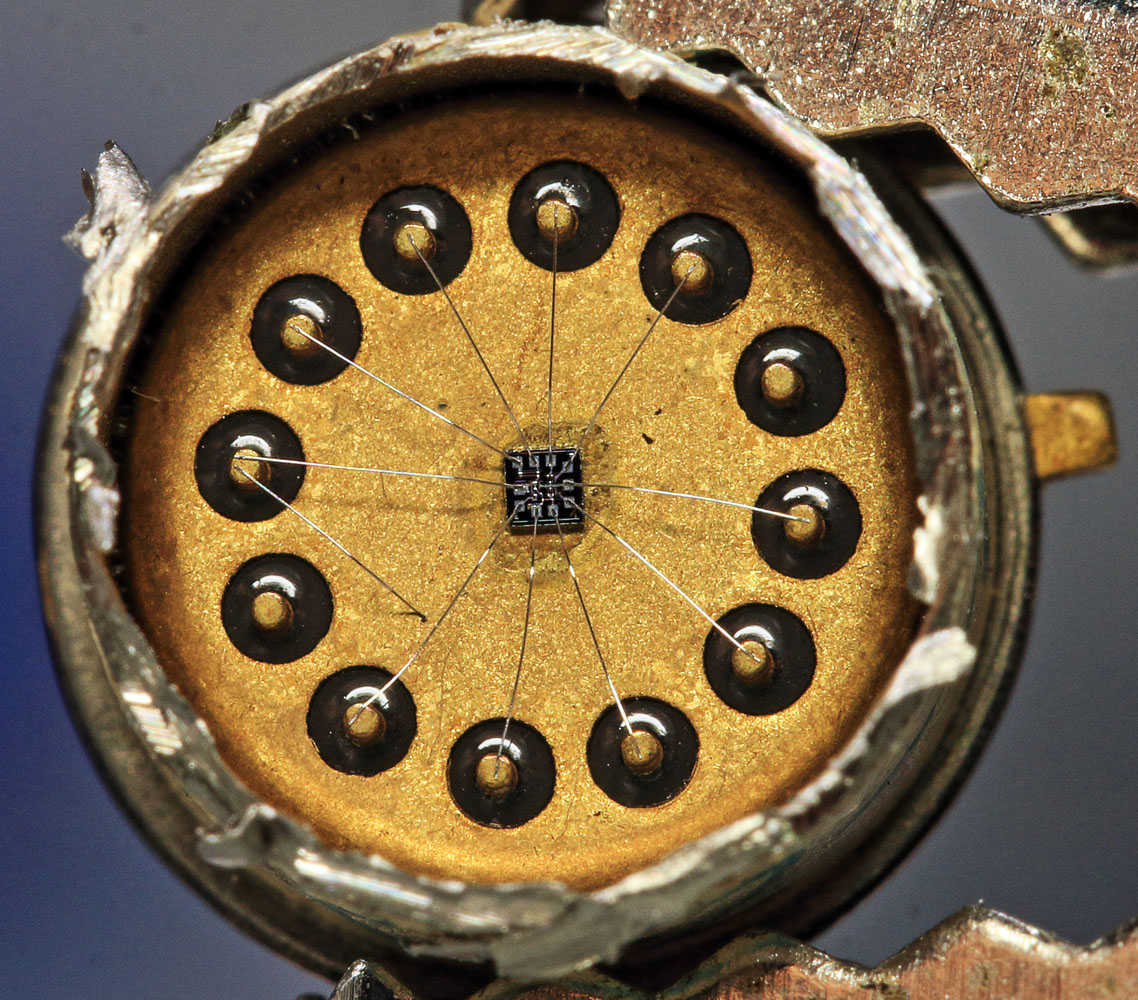

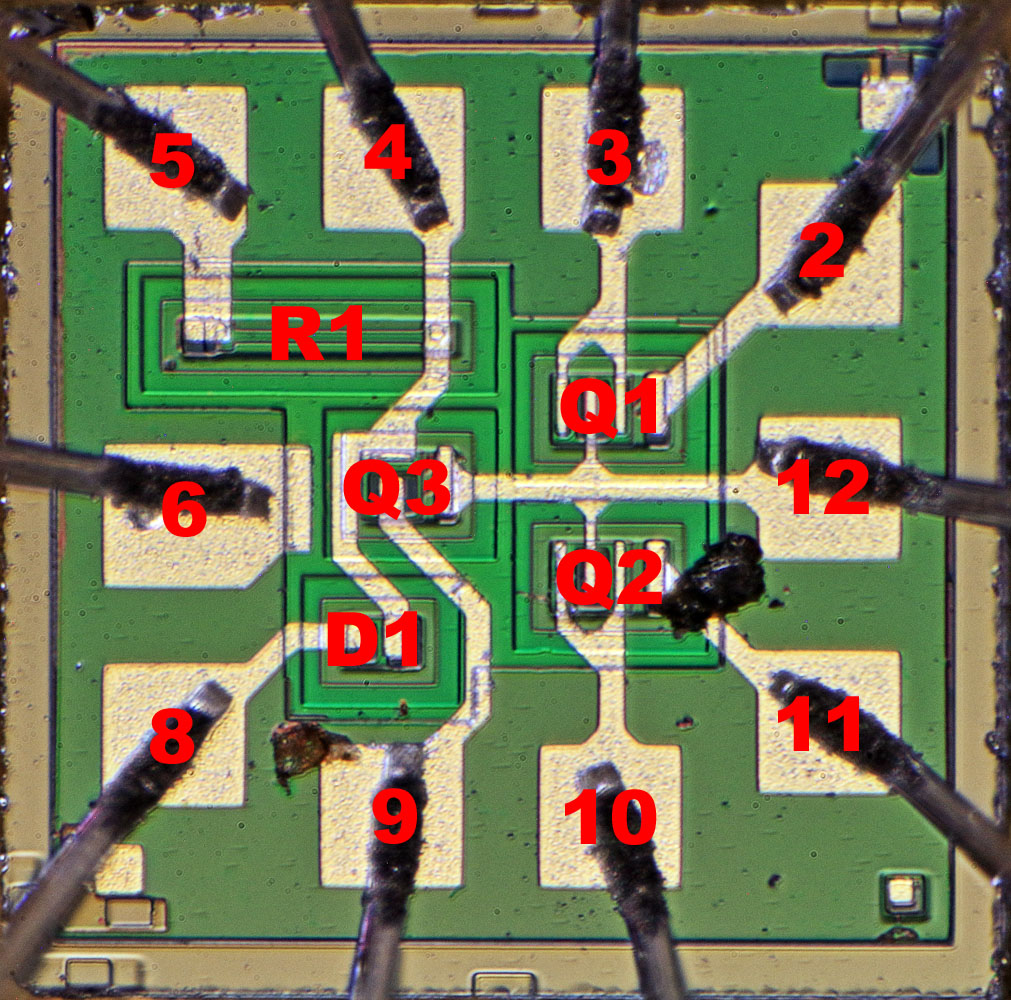

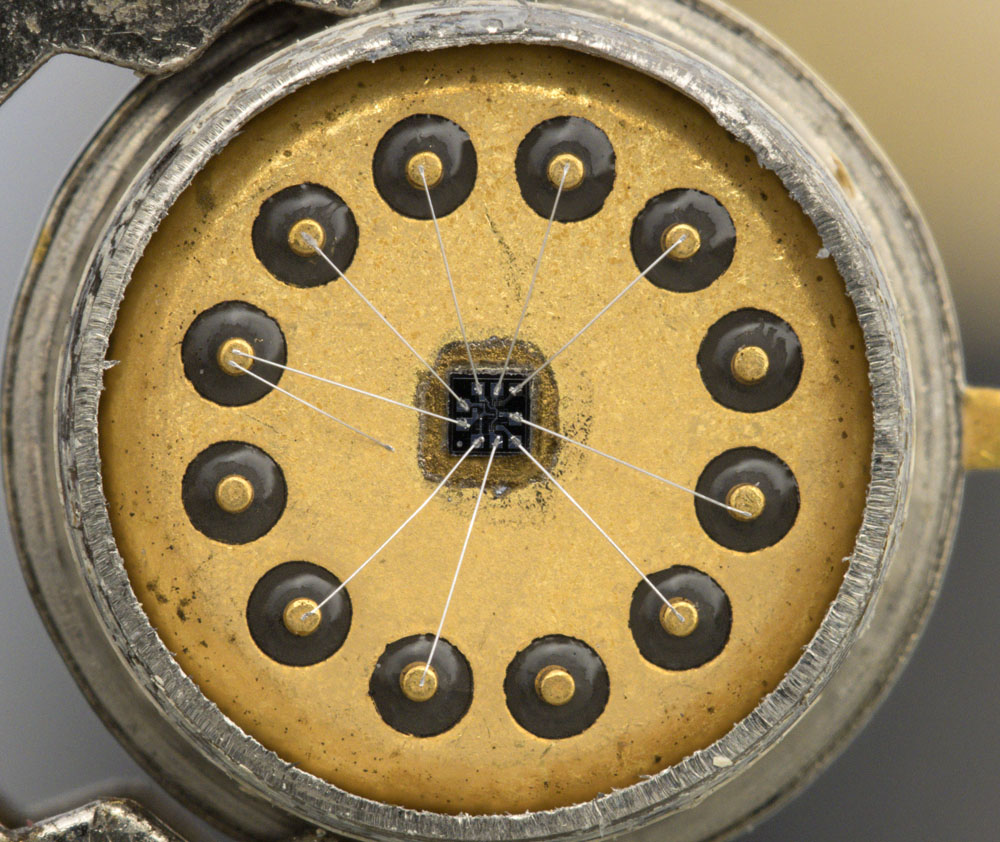

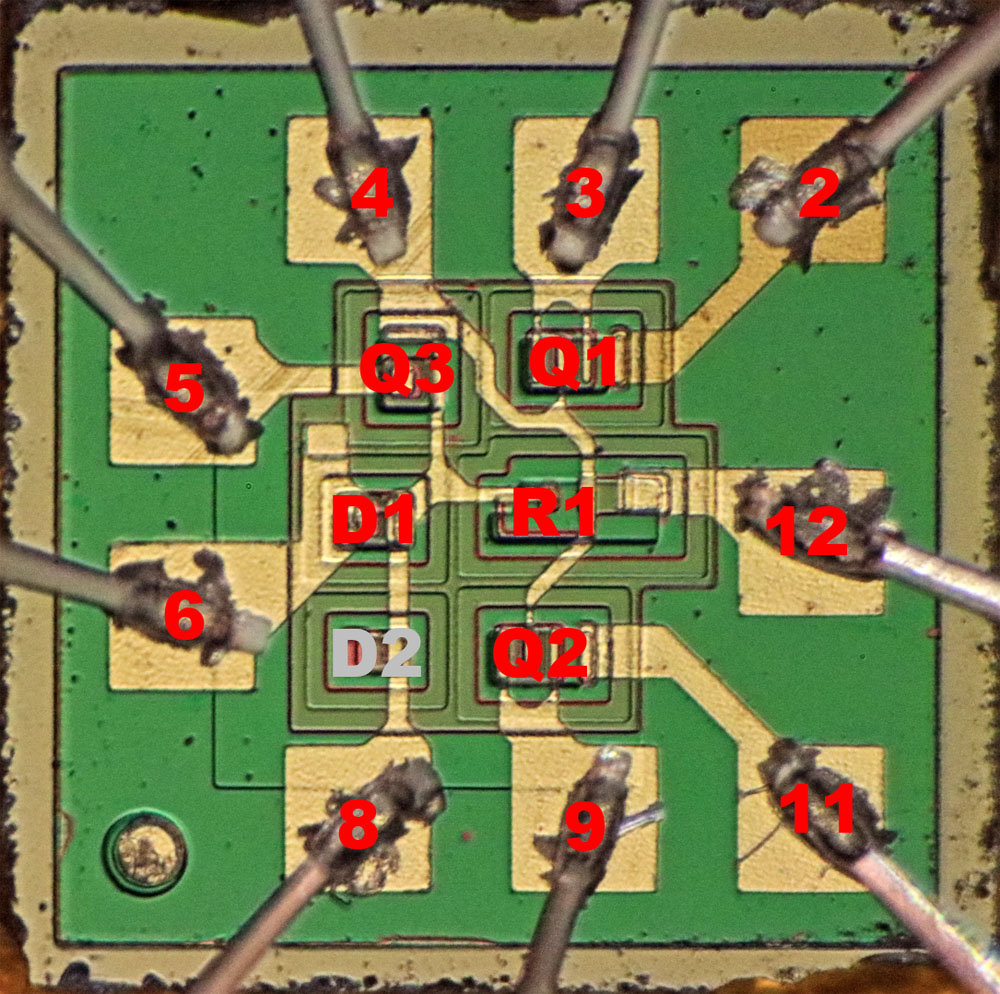

The package has 12 pins. Some of them were cut very short on this component.

Inside, it shows that 10 of the 12 pins have been connected to the die. One pin additionally defines the housing potential.

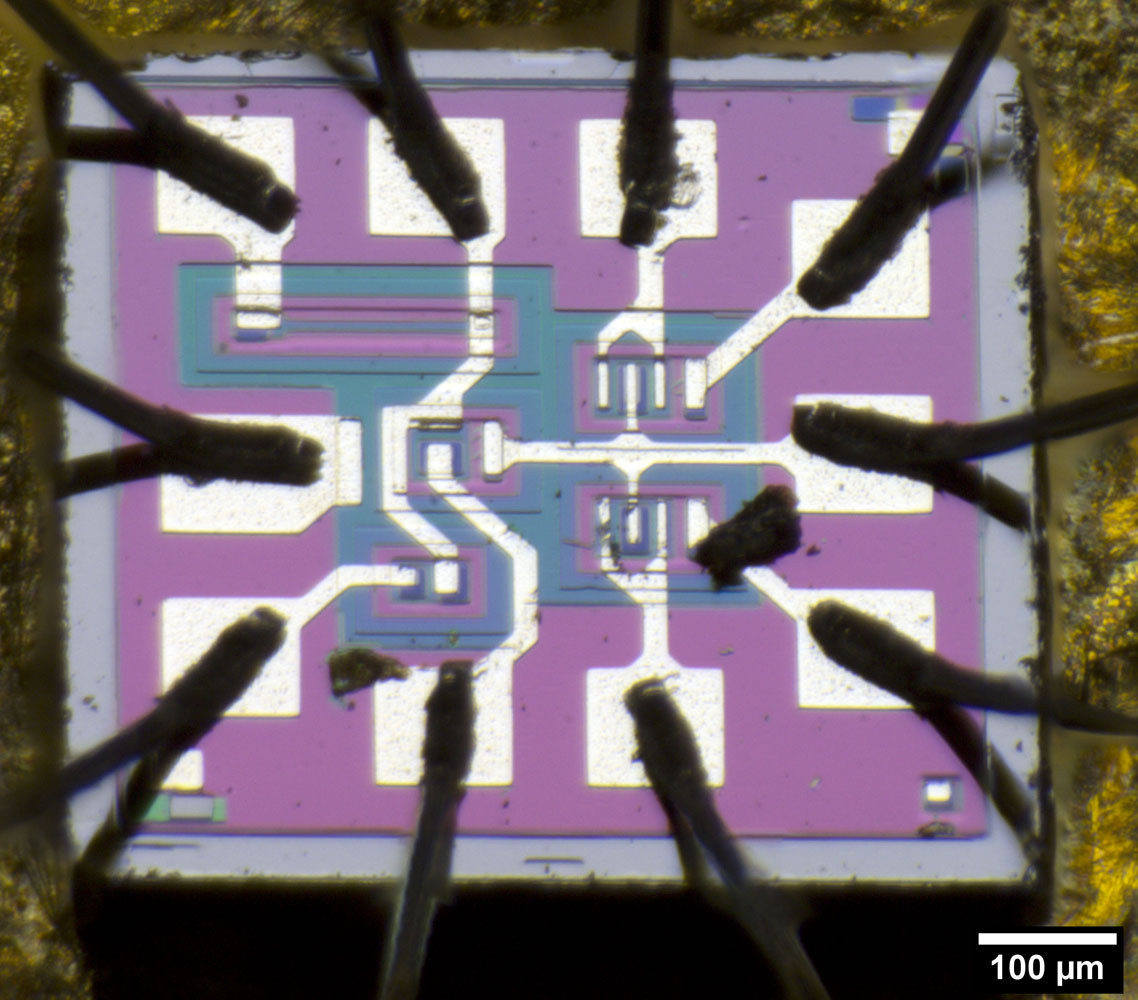

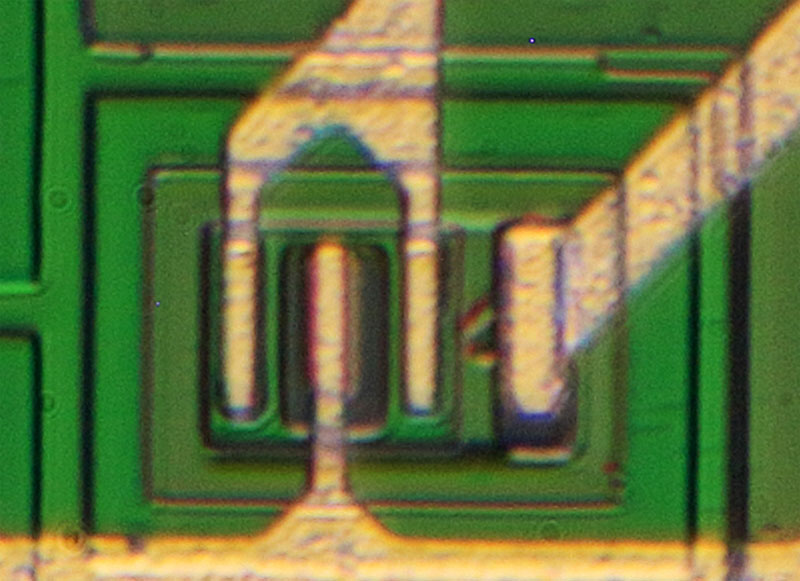

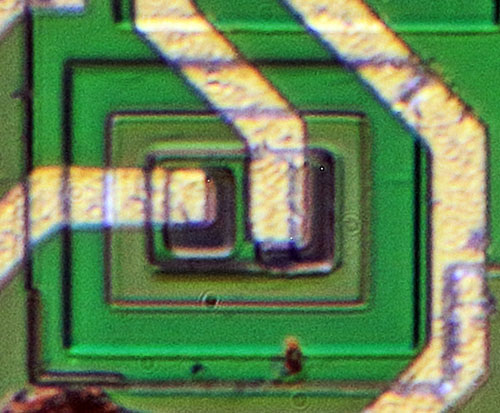

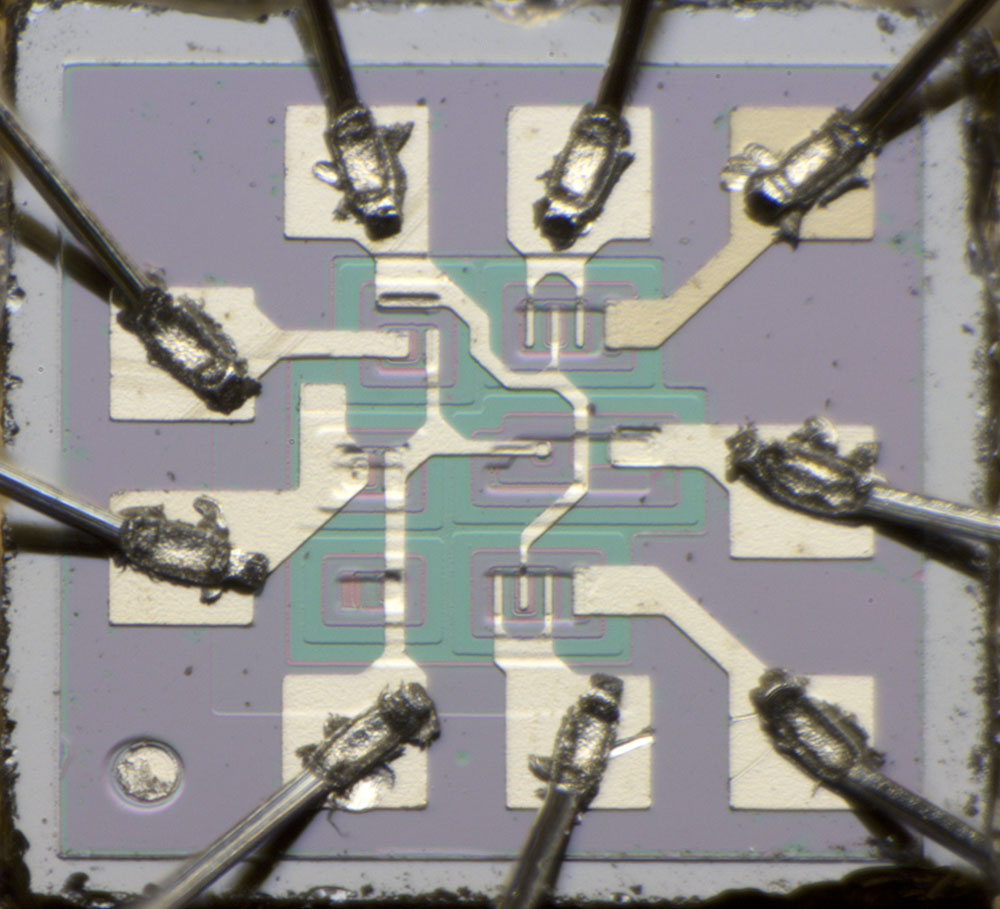

The dimensions of the die are approximately 0,7mm x 0,6mm. There are two particles on the die that cannot be removed with compressed air or by rinsing with isopropanol. Mechanical cleaning could damage the bondwires and should therefore be avoided for the time being.

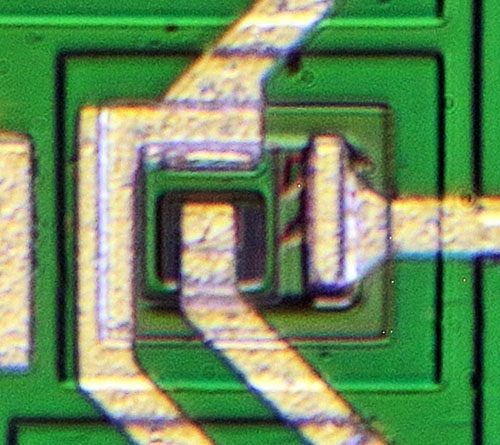

The die houses five elements. On the right are two symmetrical transistors which, with connected emitters, constitute a differential amplifier. To the left is another transistor that can be used as a current sink, for example. In the lower left corner, another transistor is connected as a diode. In the upper left corner there is a resistor.

Geometric shapes are placed in the corners of the dies, which probably facilitate the positioning of the masks and enable a check of the manufacturing process.

The minimum structure width is in the range of 5µm.

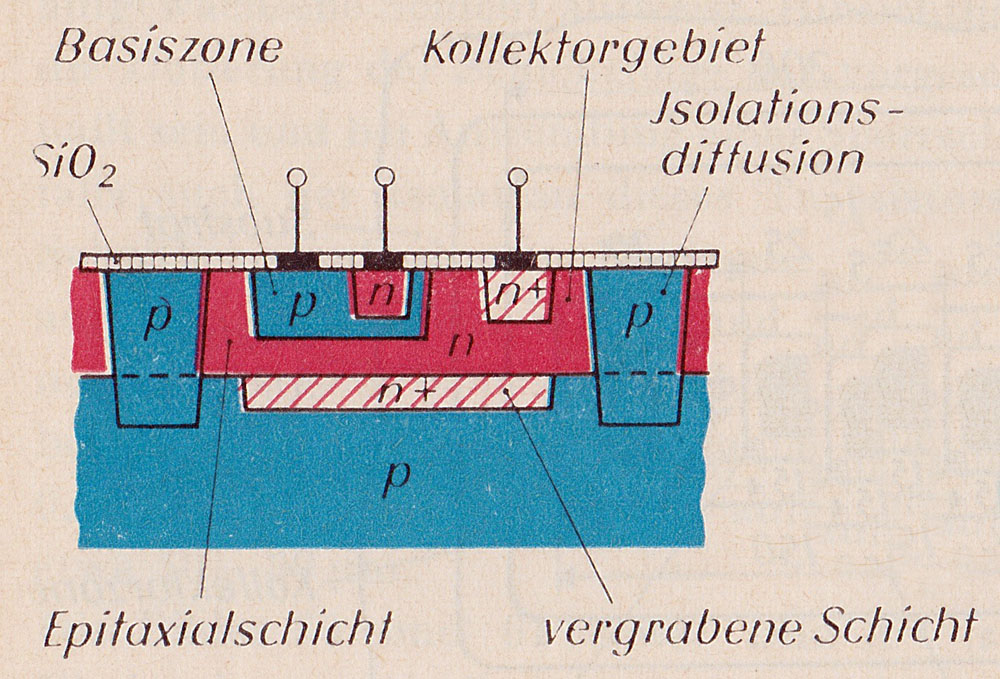

The book Mikroelektronik by W. Glaser and G. Kohl (1970, Naumburg) shows how NPN transistors were usually constructed at that time. The construction of today's bipolar transistors is not fundamentally different.

The basis is a p-doped substrate (blue). A heavily n-doped layer is created where the transistor is to be created later (red/white below). This layer later ensures that the collector potential is transferred from the collector connection to the active area with as low an impedance as possible. A uniform n-doped layer is then applied to the substrate (red), which represents the actual collector. To isolate different transistors and other elements from each other, deep, p-doped frame structures are built up. The resulting pn junctions prevent unwanted current flows across the die. Next, a p-doped base well can be placed in the delimited, n-doped collector area. Finally, the n-doped emitter area is placed inside this base well.

Between the steps described, many intermediate steps take place, which make it possible to form the individual areas as they are shown here. These include, for example, the application, exposure, partial and complete removal of photosensitive layers, the generation and removal of silicon oxide layers and various other process steps.

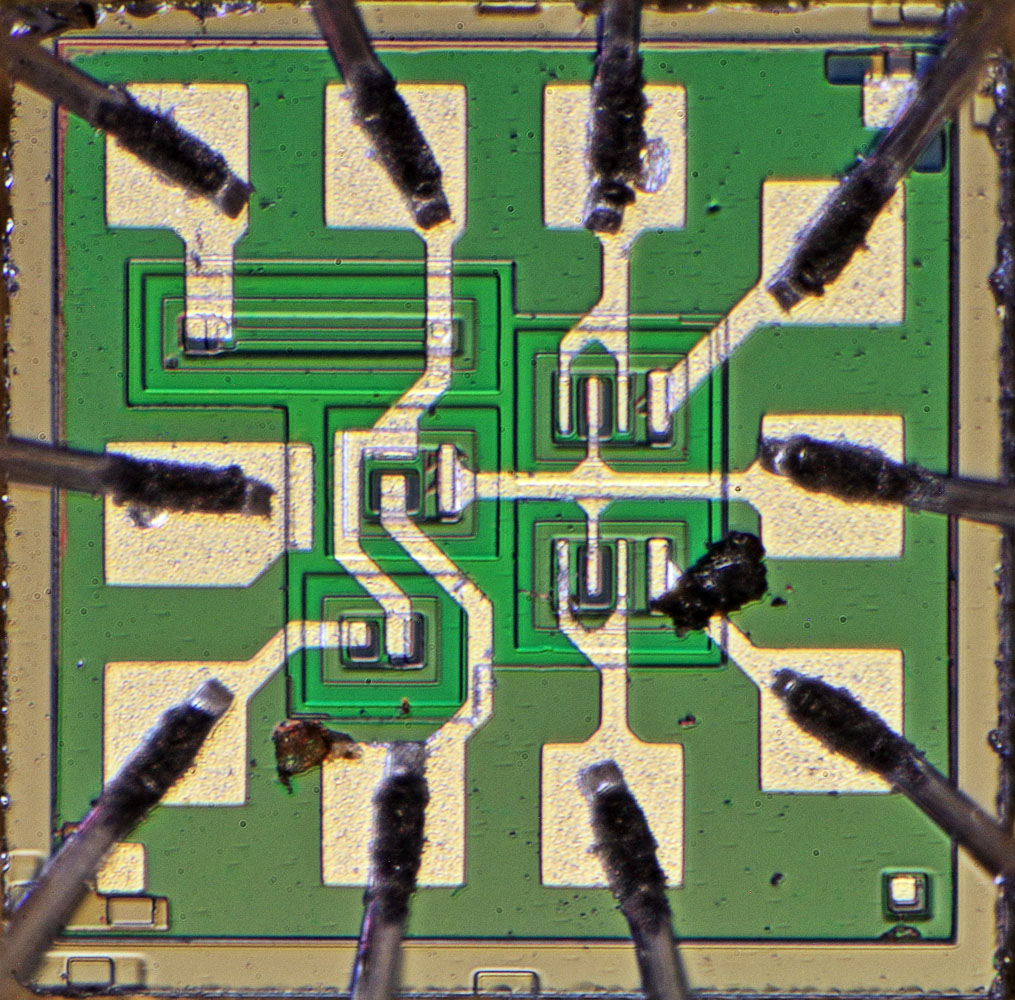

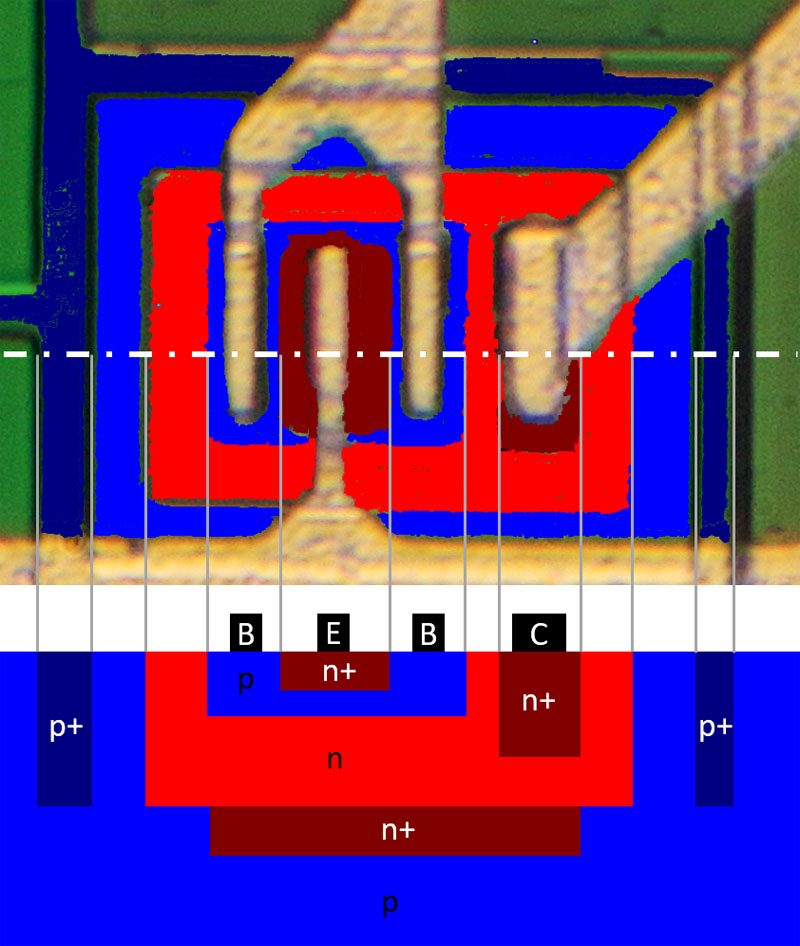

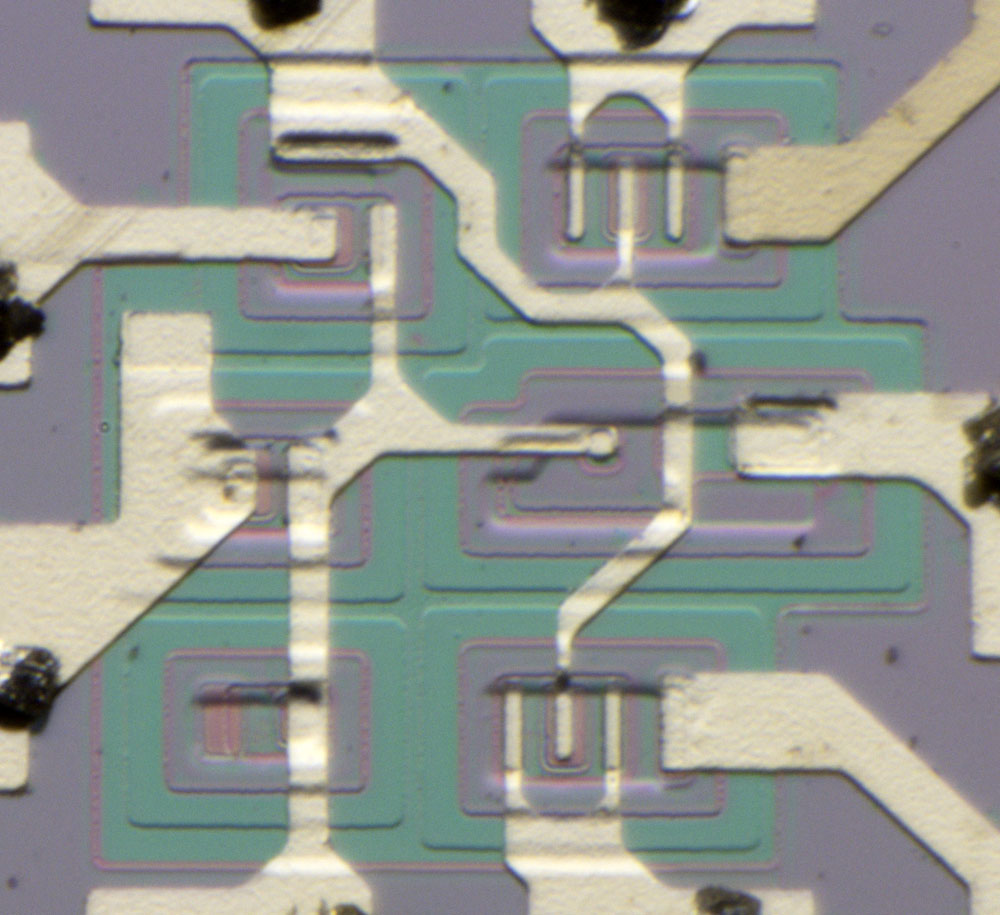

Based on the usual manufacturing process, one can try to assign the visible structures of the IK72 transistors to their functions. A coherent frame can be seen around all active elements, which certainly represents the heavily p-doped insulation. Between the n-doped collector and the isolation frame there is one more area than shown in the schematic above. Often there is still a p-doped zone around the active elements, this must also be the case here. Inside is the n-doped collector area. Below the collector connection, the stronger n-doping can be seen in the connection area. The deeper, stronger n-doping can only be guessed by outlines. To the left of the collector connection is the p-doped base area. This surface is contacted twice. This design reduces the resistance of the base contacting and thus increases the maximum possible switching speed. The n-doped emitter area is then integrated within the base area.

The third transistor, which can be used to realise a current sink, for example, has a slightly different structure than the transistors of the differential amplifier. The basic sequence of the differently doped layers is the same, but there is only one base connection (at the top) and the structure is more square, which means it takes up less surface area. Most likely, this design has a lower cut-off frequency.

In its simplest function, the transistor only controls a constant current, where slightly worse properties are hardly relevant. However, if two of the differential amplifiers are used in an analogue multiplier, the demands on the lower transistor can be as high as on the upper transistors.

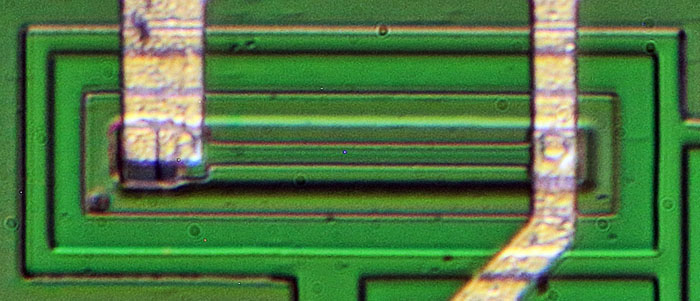

In the upper left corner of the die, a resistor was integrated.

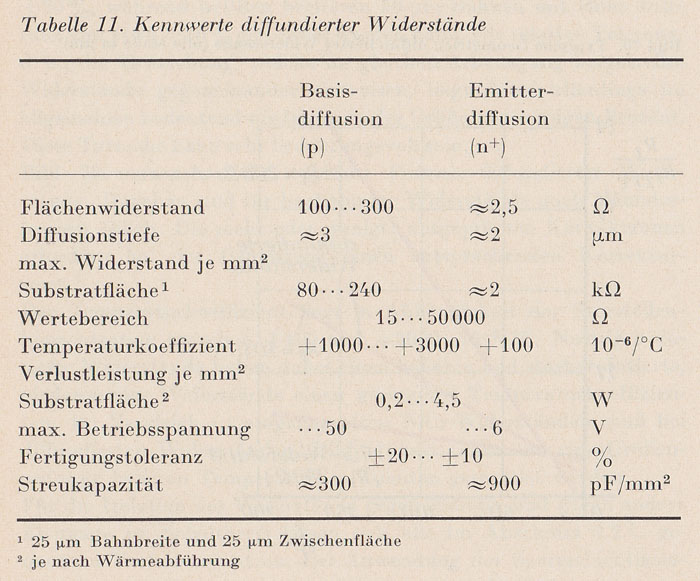

The aforementioned book Microelectronics also presents typical specifications of integrated resistors.

Resistors can be realised with the help of the p-doped base material or with the help of the n-doped emitter material. The two materials cover different resistance ranges. In the BA222 (

https://www.richis-lab.de/555_25.htm), the different types of resistors can be seen in real life.

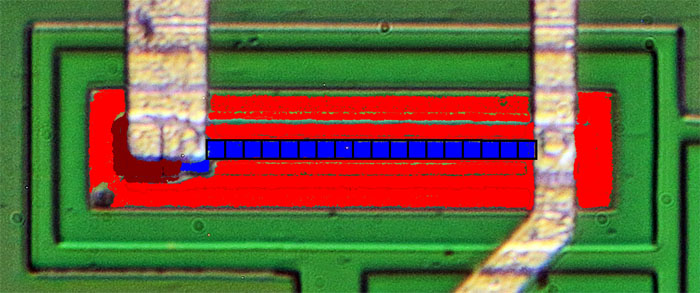

The left feed of the metal layer contacts not only the strip of base material (blue) but also a presumably strongly n-doped area (dark red). Via this path, the n-doped well (red), in which the resistor is located, is connected to a defined potential.

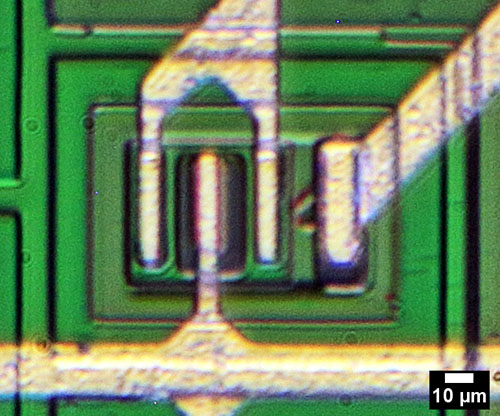

The interconnection on the die makes it possible to measure the resistor from the outside, whereby a value of 2,08kΩ can be determined. There is room for 18 squares in the area of the resistor. With the 2,08kΩ, this results in a specific resistance of 116Ω/sq, which fits quite well with the above characteristic values for a basie diffusion.

The dimensions of the resistor can even be used to estimate the load capacity. With a length of 140µm and a width of 9µm, this results in an area of 0,00012mm². According to the table above, you can expect a power handling of 0,25mW to 5,7mW. What sounds like a very low value can be quite sufficient at the base of a transistor.

At the base of the lower transistor there is a transistor connected as a diode.

The substrate is contacted by its own pin. The exclusive connection enables the substrate to be connected to a lower potential than is available in the IC itself. As a result, the pn interfaces that isolate the transistors from each other widen, less leakage current flows and parasitic capacitances are reduced.

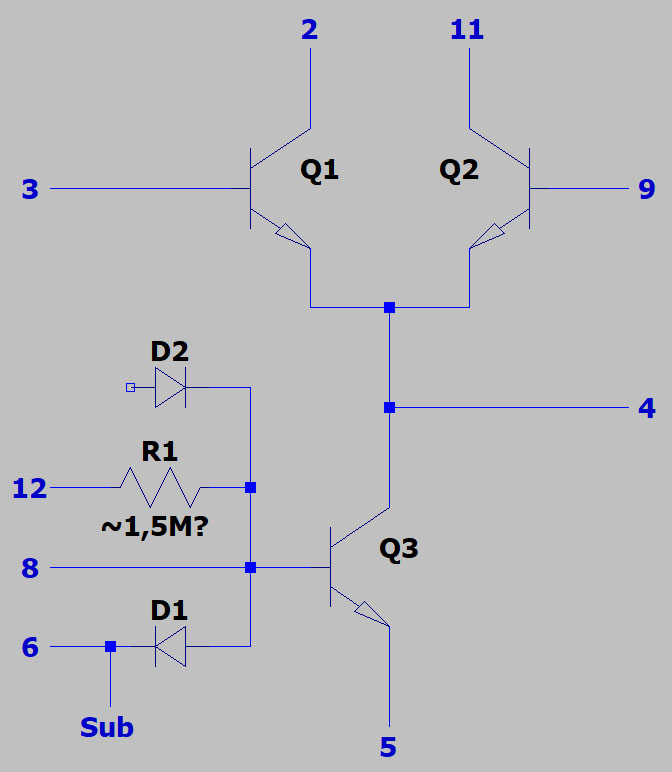

In summary, this results in the circuit shown. The IK72 represents a differential amplifier with a transistor in the emitter path. Transistor Q3 can be used as a current sink or a signal can be applied to it and an analogue multiplier can be built with a second IK72.

The base of transistor Q3 has multiple connections. Pin 4 allows a direct, low-impedance feed-through to the base. Alternatively, resistor R1 can be used as a base resistor. The diode D1, connected in parallel to the base resistor, could make it possible to accelerate the switchoff of the transistor. With this parallel connection, more current can flow from the base, the free charge carriers are discharged more quickly and the transistor switches off faster. However, it is more likely that the resistor and diode in the circuit were used as a current sink to make the current value less dependent on temperature. The temperature drift of the diode then reduces the reference voltage at the base at increased temperature and thus compensates for the drop in the base-emitter voltage of transistor Q3.

This part should be an IK72 too. The casing matches the casing of the IK72 above. Only the characters "A 05-2" are printed on the paper band. The sequence of characters shown on edge cannot be identified with certainty. It could be the numbers 055.

Superficially, the internal structure is the same as that of the IK72 above. However, pin 10 is not connected to the die.

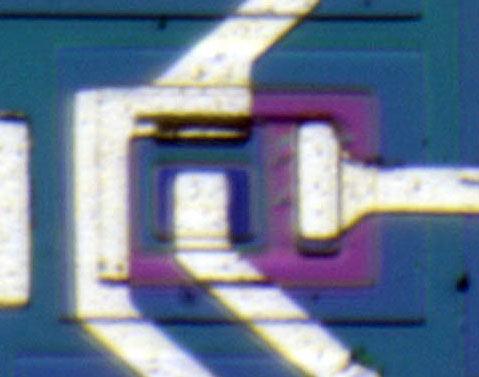

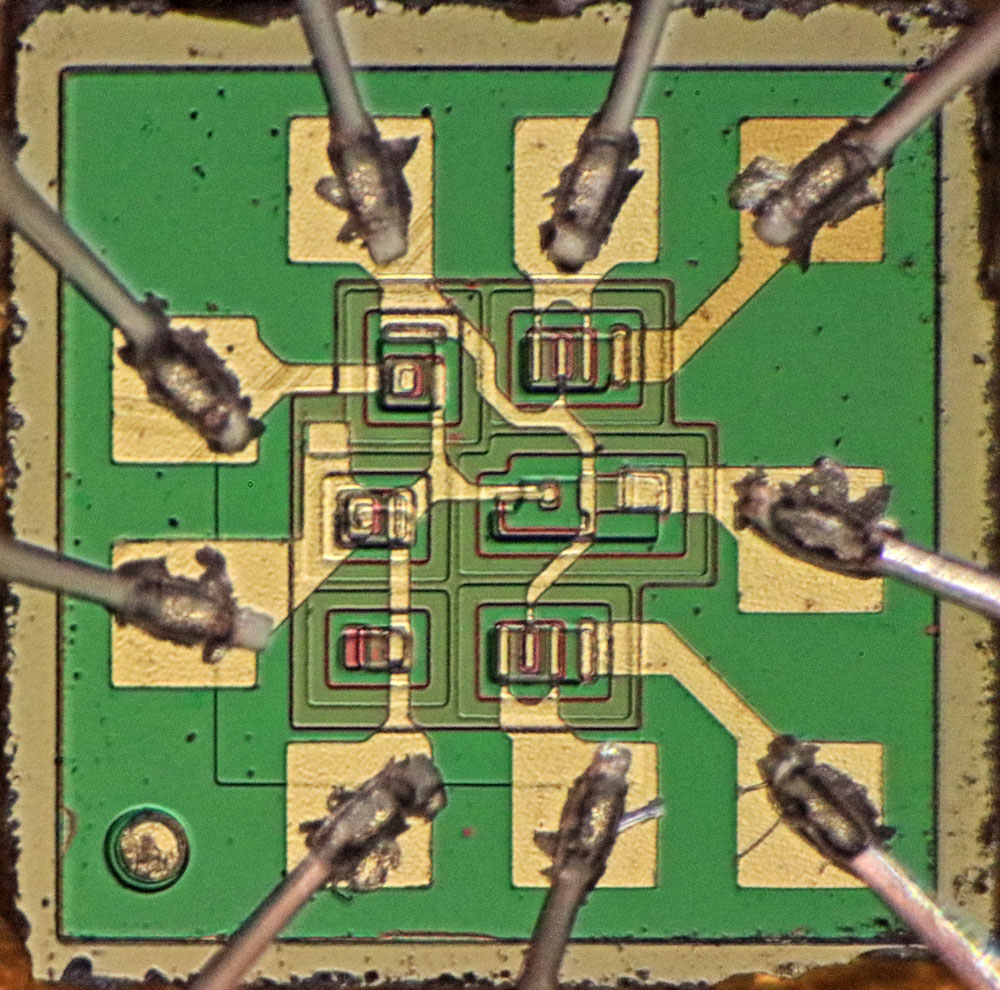

The edge length of the die is 0,8mm. The construction of the circuit is similar to the IK72 above. In detail, however, there are clear differences.

Unlike the IK72 above, here pin 10 is not connected to the die.

The circuit is basically the same. It is a differential amplifier with some options at the base of the common current sink Q3. The construction and placement of the input transistors Q1/Q2 is the same as the IK72 above. The pinning in this area is similar. However, the remaining pins are pinned significantly differently.

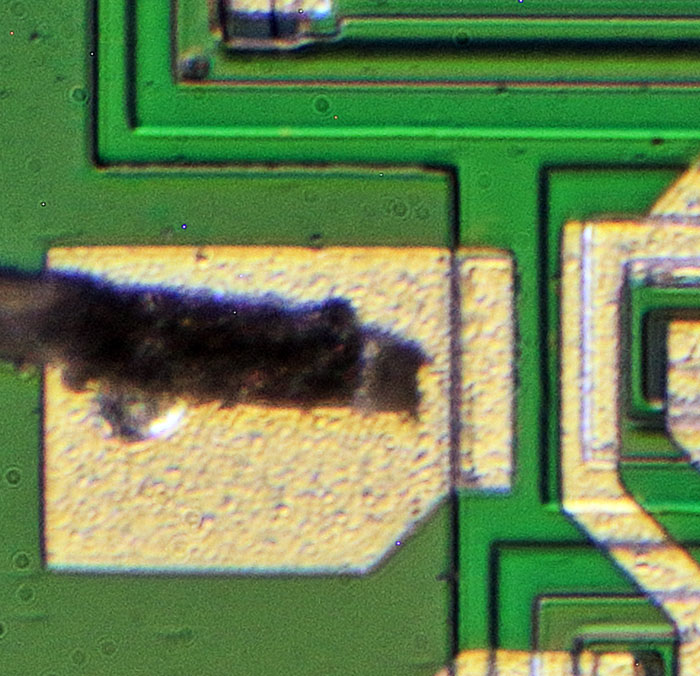

The resistor R1 at the base of transistor Q3 seems to have a surprisingly high resistance value of 1,5MΩ. Perhaps such a high value was not desired. At that time, the integration of resistors was not yet mature.

In this component, there is no separate substrate connection. Instead, pin 6, which contacts diode D1, is additionally connected to the substrate. The die provides an additional diode (D2), but it is not integrated into the circuit.

Perhaps this component is an earlier version of the IK72 or a further development.

The structures of the transistors are clearly visible in detail. The diode D2 seems to have been integrated as a diode only. A collector connection for using the structure as a transistor is not visible. The resistor R1 appears very thin. This would fit the high resistance value.

https://www.richis-lab.de/IK72.htm