Hi,

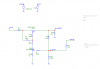

I simulated this circuit in MicroCap, a simple switch using a NMOS (NX138BK) and a PMOS.

I get those results :

Normally, I would expect VLOGIC to become 3.3V when VTRIG switches to 3.0V (0 -> 3V transition).

The PMOS being high impedance, it should be to ground until the VTRIG applies a voltage at the gate which should then close the NMOS and thus close the PMOS so that 3.3V can appear at VLOGIC.

Except it just doesn't happen. As soon as 3V3 starts (0 -> 3.3V), VLOGIC goes to 3.3V.

Could someone rationally explain what is happening?

And perhaps a solution?

I tried different PMOS, but in vain (greyed out ones).

I have attached the .cir file (MicroCap file). It is portable, thus the models are embedded in the file.