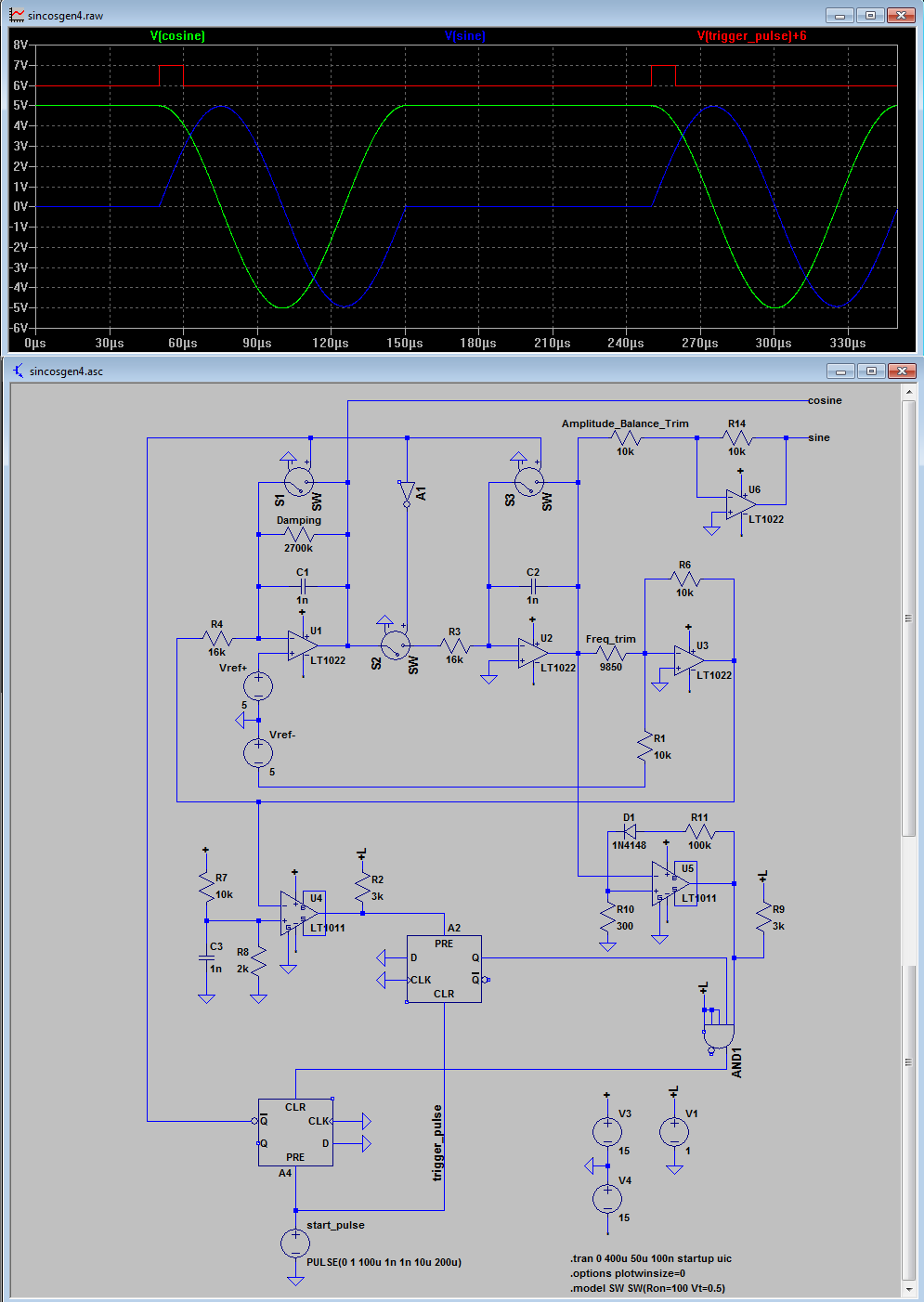

Here is a pretty complete simulation of the polar-coordinate oscilloscope timebase that I have developed:

Some brief notes:

Assuming equal R and C values for the two integrators and a unity gain inverting stage, the frequency of oscillation is equal to 1/2piRC.

Oscillation happens at the frequency at which the gain around the loop is equal to 1. The operating frequency can therefore be trimmed by tweaking the gain

of the inverting stage only. However this will result in a small amplitude imbalance between the sine and cosine waveforms (however they will always be in "perfect quadrature". This needs to the trimmed separately and externally, in an stage outside of the feedback loop.

Another thing that will cause an amplitude imbalance between the sin and cos waveforms is a C and/or R variation between the two integrator stages. I use 0.1% resistors for R so the greatest/actually significant source of error is in the capacitor tolerances. The resultant amplitude imbalance is directly proportional to the capacitor value imbalance.

In my timebase, I switch decade ranges by switching different value timing caps. There are 3 decade ranges. The range switch is a 4-pole 3-position rotary. Two of the poles are used to switch the integrator capacitors. The third pole is use to switch one of three gain-adjusting trimpots in the inverting stage feedback so that the operating frequency ("sweep" period) can be accurately trimmed for each range. Finally, the 4th and final pole of the range-selecting rotary switch is used to select one of another three trimpots that accurately trim the amplitude balance between the sin and cos waveforms for each range.

I implemented the initial condition setting in a manner that results in no amplitude glitching of the desired signals. Analog switches are used to short the integrator capacitors and a +5V initial condition for the cosine integrator is achieved by elevating the virtual earth of the integrator to +5V with a precision reference. Note that I have used an additional analog switch to disconnect (when initial conditions are forced) the summing junction of the integrator from which the sinewave is derived. This prevents the current that would otherwise be forced into this integrators summing junction by the +5V initial condition of the preceding (cosine) integrator stage from developing an DC offset error at the output of this integrator due to the non-zero on-state resistance of the analog switch shorting the integration capacitor.

The circuit can be likened to a simplified state-variable oscillator without the damping feedback and amplitude servo control. In theory, with ideal integrator stages, the circuit would oscillate indefinitely at a constant amplitude as initially defined by the initial conditions. However due to the finite gain-bandwidth product of real op-amps as used for the integrator stages, in this particular circuit, the Q-multiplication effect will always result in amplitude growth with time.

If allowed to oscillate for enough number of cycles, the amplitudes of the sin and cos terms will eventually grow until the amplifiers clip and they become square waves.

While this isn't an issue in the design here as only the first cycle of oscillation from the initial conditions is used for the oscilloscope sweep before initial conditions are reinstated, at higher operating frequencies I have found the amplitude growth over just one cycle to be significant (in the order of 0.5-1% at 10kHz). When potting a circle on the oscilloscope using these sin and cos terms, this results in the end point not meeting up exactly correctly with the start point.

However there is a simple fix to the problem. Trim-able negative damping (to precisely counter the amount positive damping due to Q-multiplication) can be applied with the simple inclusion of a high value trimmer resistor in parallel with the capacitor of the integrator from which the cosine term is derived only. This resistor is the one labeled "damping" in my simulation schematic.

In each range, I switch frequencies in three 1/2/5 steps, by switching fixed 0.1% tolerance R's for the integrators (16k, 32k and 80k). This requires and other rotary switch - 2 poles, 3-positions. There is therefore a total of 9 (3x3) calibrated timebase frequencies (50mS to 100uS). Switched integrator capacitors are 1, 10 and 100nF.

I have attached the LTspice simulation file (renamed *.txt once again). It includes a simplified logic simulation of the comparator an digital elements required to automatically detect the end of one complete "sweep" cycle and re-instate initial conditions in idle mode, until the next sweep trigger input pulse occurs.

So there you have it; that should be everything that you need to know to implement a timebase for your experimental polar-coordinate or phasor-display oscilloscope.

EDIT:

I have noticed one small error/infelicity in the simulation. For the hysteresis of zero-crossing detector/comparator U5 to work correctly (so that in real life the detector does not oscillate away while the sine term is maintained in the initial condition mode (0V) ), the open-collector pullup resistor R9 will be tied to +15V rather than +1V. 1V is used in the sim for the logic high level as this is the default in LTspice for the "special function" digital logic elements.