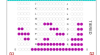

My partner and i recently attempted to purchase two tickets to a show but the ticket booking software would not allow me to select my preferred seats (N9 and N10 in the attached seating plan)

because that would have left one isolated seat (N11).

In my opinion, while I can accept that it might be desirable to minimise the creation of multiple isolated seats in a row, the application of this rule in this particular scenario is not sensible. It leads to the following consequences:

The seats in row N in the centre section can only be sold in the following circumstances:

1. A single person can book seat N9 or N11 (but not N10). Then two people like ourselves would be able to book the remaining 2.

2. A single person can book seat N9 or N11, but then another single person could not book one of the remaining two seats.

3. Three people can book seats N9, N10 and N11 if they buy them at the same time.

Similarly for rows O and P.

Worse still, nobody can buy eight tickets in row R as that would also leave one isolated seat

I suspect that the requirements that were given to the programmer were too simplistic. Given the following definitions:

- nIsolatedSeats = the number of empty seats in a row that are not next to an empty seat

- nOccupiedSeats = the number of seats in a row that are not empty

- nRequestedSeats = the number of adjacent seats requested in the current booking. Can't be greater than the number of adjacent empty seats.

- nEmptySeats = nOccupiedSeats - nRequestedSeats = the number of empty seats remaining if the current booking is confirmed

The current algorithm appears to be something like:

AllocateSeats(nRequestedSeats)

if (nIsolatedSeats > 0) then RejectBooking else ConfirmBookingMy preferred solution that would avoid the questionable situations described above would be:

AllocateSeats(nRequestedSeats)

if (nEmptySeats > 1) and (nIsolatedSeats > 0) then RejectBooking else ConfirmBooking

Am I on the right track?

Recent Posts

Recent Posts