Hi guys, I am working on repairing a waveform generator and I could use some help debugging the PLL.

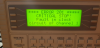

The reason that I am suspecting the PLL to be the issue is because of an "unlocked" light(LED201B) and because of the clock circuit error message shown below. There is only one other clock that I can find(a 10MHz xtal, and that is supposedly running just fine.

Here is a schematic of the PLL - I have colored the trace names according to the scope channel colors of the ANALOG waveform below(not the digital one).

First step in debugging is looking at the control inputs of IC212B, which is an MC145170-2:

https://www.nxp.com/docs/en/data-sheet/MC145170-2.pdf The control inputs are supposed to send a number of clock pulses to set the internal registers of the IC, which then compares the 10MHz clock with the clock from the LC filter. But the control inputs do not send anything but a short pulse on all channels:

This puzzles me a bit, as there is no description of the default behavior of the IC in the datasheet. I don't know if the "missing" programming pulses are caused by a different issue also causing the clockcircuit error and hence not trying to lock the PLL, or if whatever default output is missing from the PLL and hence triggering the error.

Anyway, the result of the MC145170-2 is a series of pull-up or pull-down pulses on pin 13(yellow). These are then fed to the integrator(IC214B), which then controls the voltage applied to the varactor diodes, changing the oscillator frequency until stable. At least, that is my understanding.

Probing the analog circuit reveals the following behavior.

At first, it is clear that the output of the integrator(blue) is acting until the input from pin 13(yellow) has reached the reference voltage of the non-inverting opamp input(thats about 1.6V). When that happens, the integrator output drops to zero. But as the integrator input dorps, so should the bias voltage on the varactor diodes(magenta).. Right? It stays at approx 2 diode drops, which makes sense if you consider D201B and D202B. But why isn't it pulled back down, as the integrator output drops to zero? Even stranger is what happens after ~15 seconds, as seen in the second waveform. YELLOW and BLUE drops to zero once MAGENTA has climbed all the way to 2 diode drops.

I am unsure of this behavior.. Am I missing something in my understanding of the PLL circuit? Is there something that comes to mind when you look at the waveforms that just screams "this isn't working"? Is there something on the schematic that you think I should look closer into?

Just to mention it: Yes, I verified all voltages. The 10 MHz reference waveform is injected to pin 1 of the MC145170-2. It is present and is good.

Thank you for your time!

Edit: Sorry, I am somehow unable to figure out how to insert the attachments as inline pictures! I hope you can deduce the order from the numbers