OK, I have been messing with this over the weekend, and despite adding various things like capacitive coupling with a Schottky diode DC recovery between driver and FET gates, and jancumps dead time introducing add ons, I am still losing FETs.

What do you guys reckon to this discovery though?

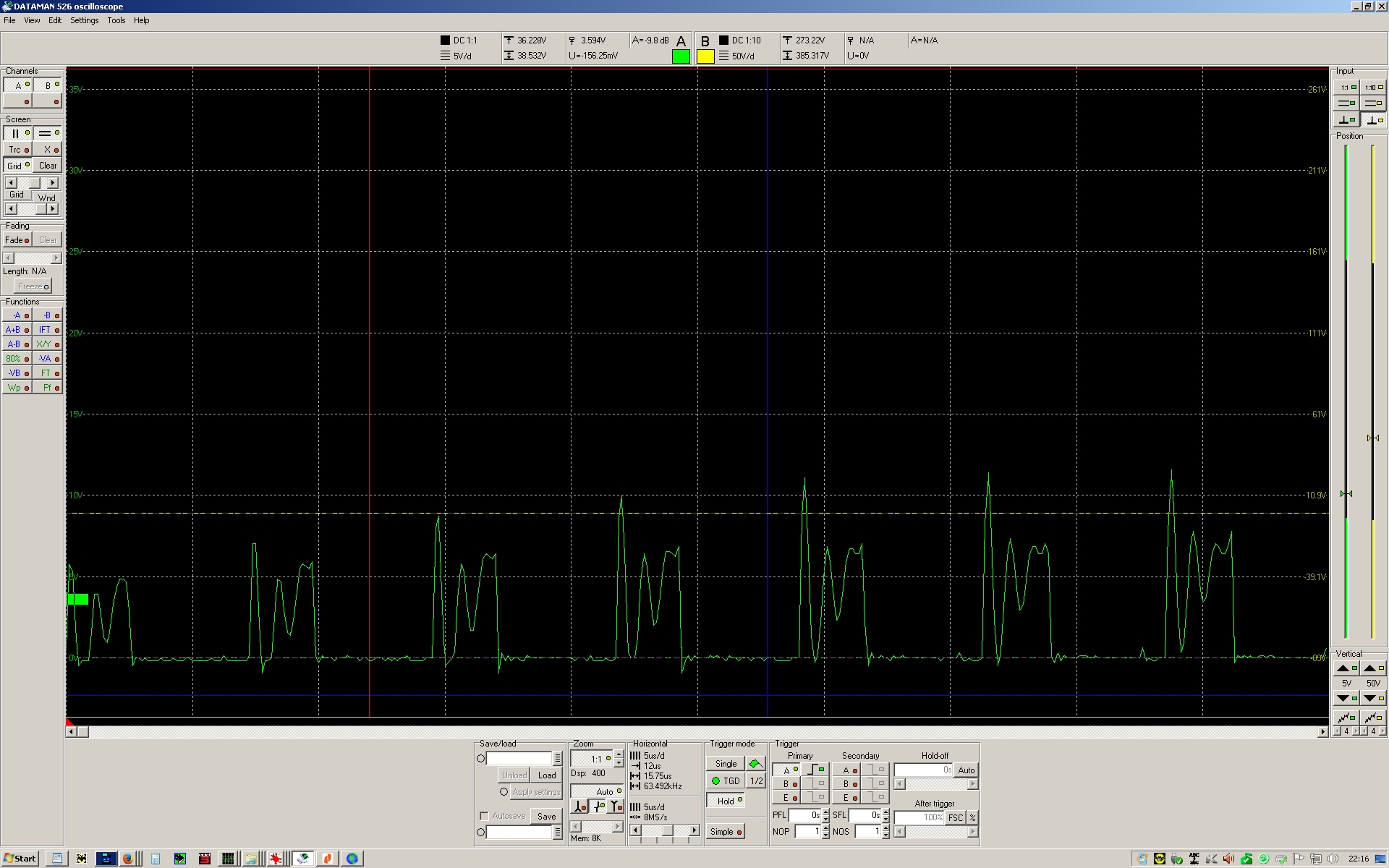

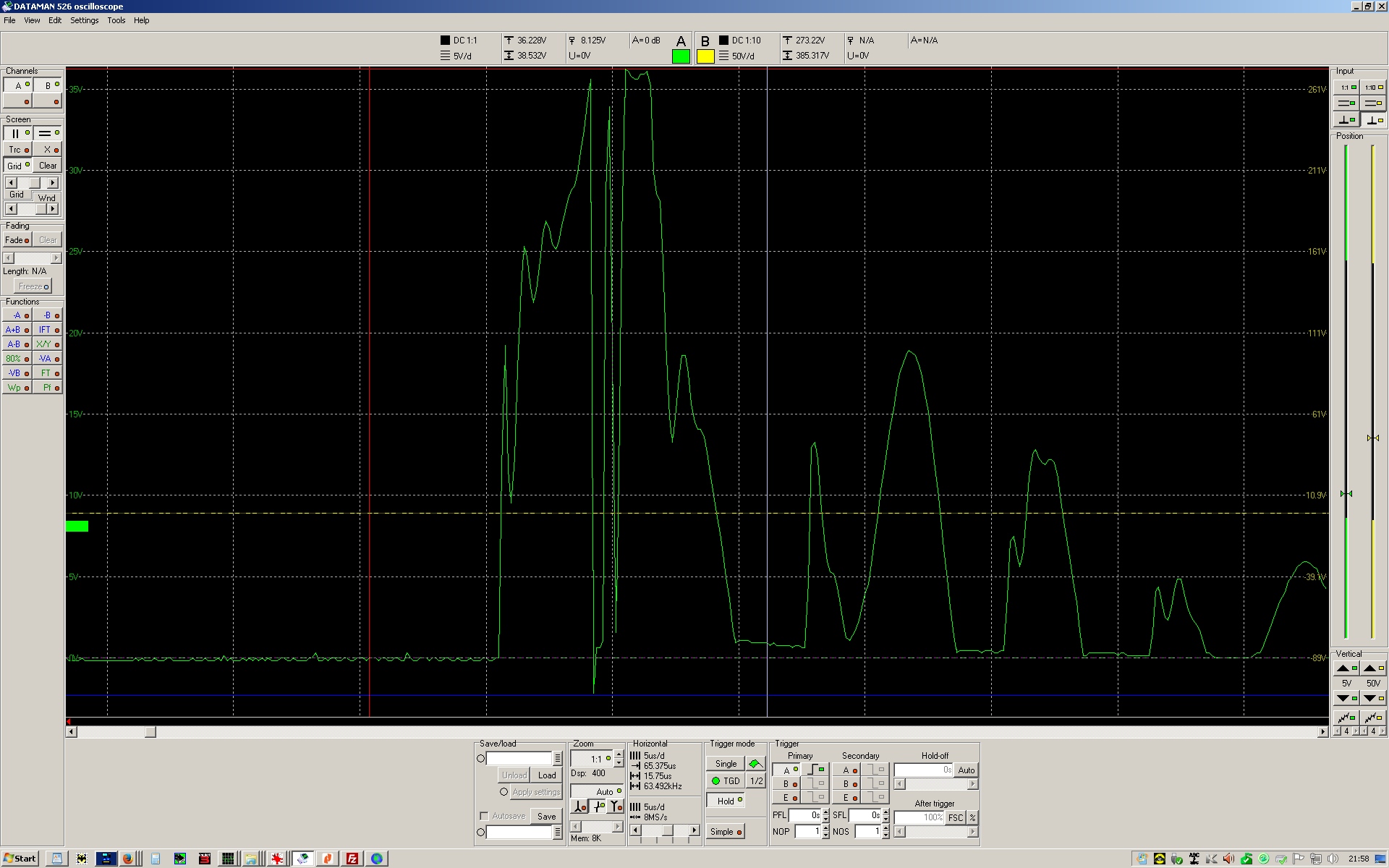

Right, I think I finally may have a handle on this and it could be transients. When a transmission starts I never seem to have a failure that I can recall. It's when a transmission ends. The amp has 12V and 50 or 100V permanently on. The transmission is solely instigated and ended by starting and stopping the drive signal. When I scope the drain to source pins with a proper pigtail as the ground on my probe, set to X1 but with a X20 attenuator I use for automotive work, I see these captures. A TX starts nicely. A ceasing of a TX, even into a Bird 400W dummy load often shows one or more transients up to 770V in the worse cases, well over the FET's rated drain to source voltage limits. Sometimes one pulse, sometimes three or more over about a 70uS time frame. I can only show part of the capture of course. Bear in mind the voltage axis figures need multiplying by X 20!

Am I right thinking this could kill a FET? Would a TVS diode be happy across a drain / source running at 136kHz? Would it be fast enough to catch such pulses? Is there another way to quell the pulses? Thanks!! First image is the start of a TX session using WSPR. Second image is the drain / source capture when the same transmission ends.