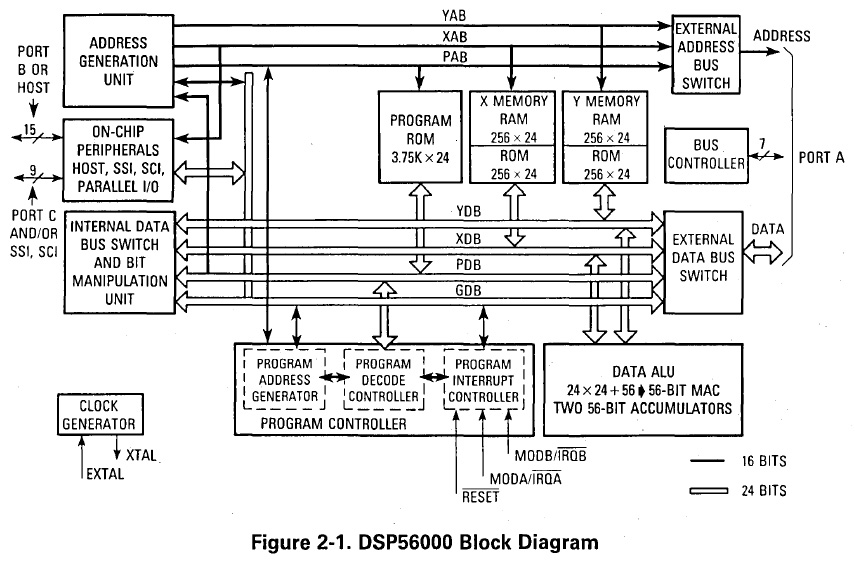

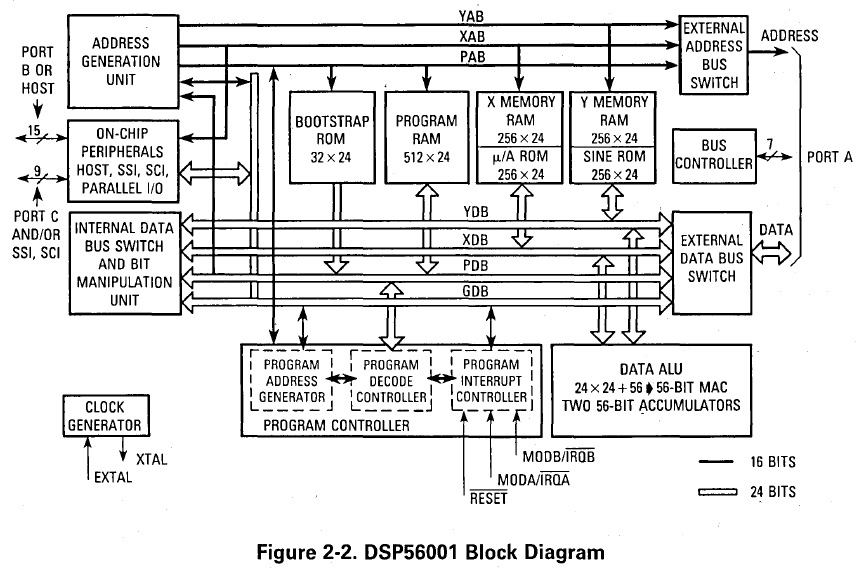

The DSP56000 is a signal processor introduced by Motorola in 1986. The processing unit handles 24-bit numbers at up to 20,5MHz (in the first place). While the DSP56000 was mask-programmed, Motorola produced a variant, the DSP56001, that could be programmed by the user. To do this, the program ROM was replaced by a 512x24 RAM. The remaining bootstrap ROM controls the programming of the chip. In addition, the DSP56001 has a µ-law, an A-law, and a sine table.

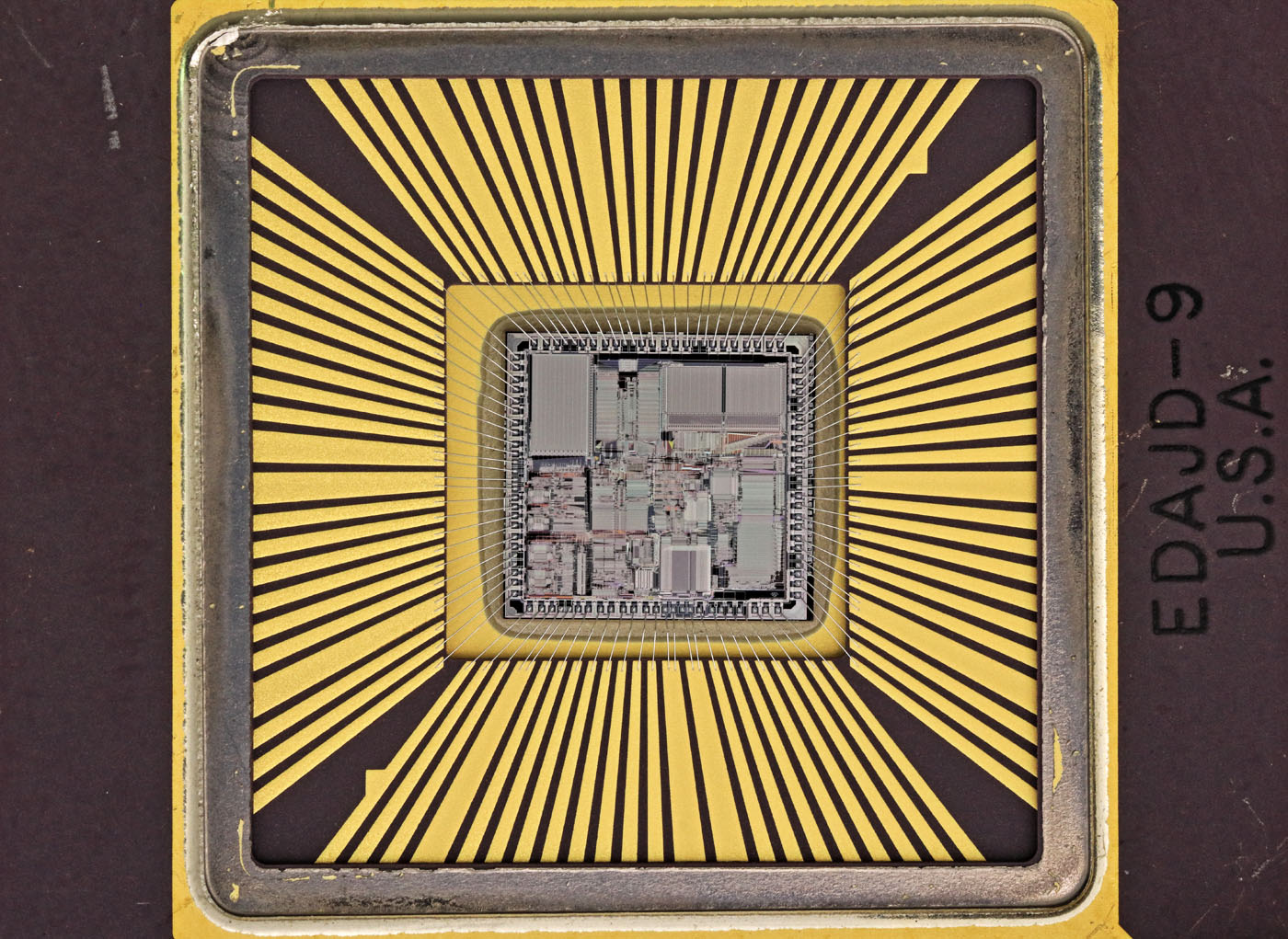

Here you can see an XSP56001RC20. The X indicates that the design has not yet been fully qualified. The abbreviation RC20 indicates the maximum operating clock for which the part is specified. In addition to the 20,5MHz clock, there were variants with 27MHz and 33MHz. As will be shown later, C68S stands for the mask revision used. 9104 could be the datecode, which would then refer to the year 1991.

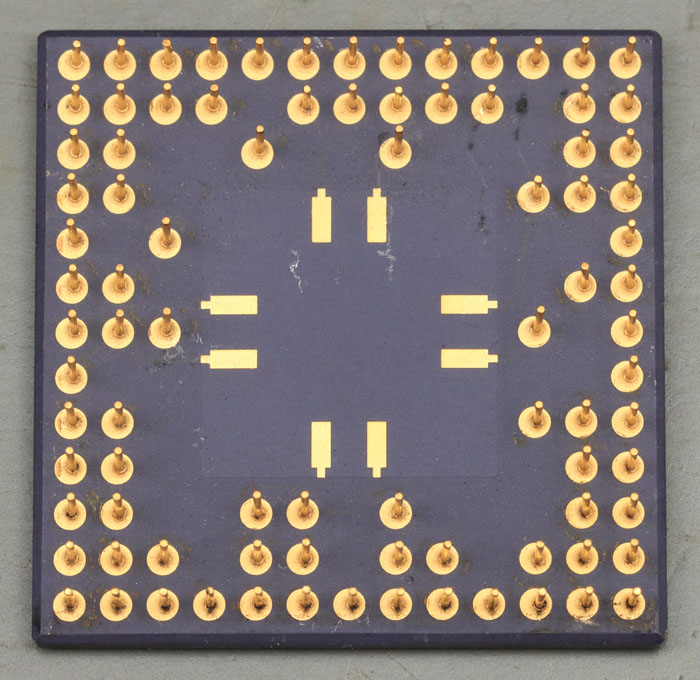

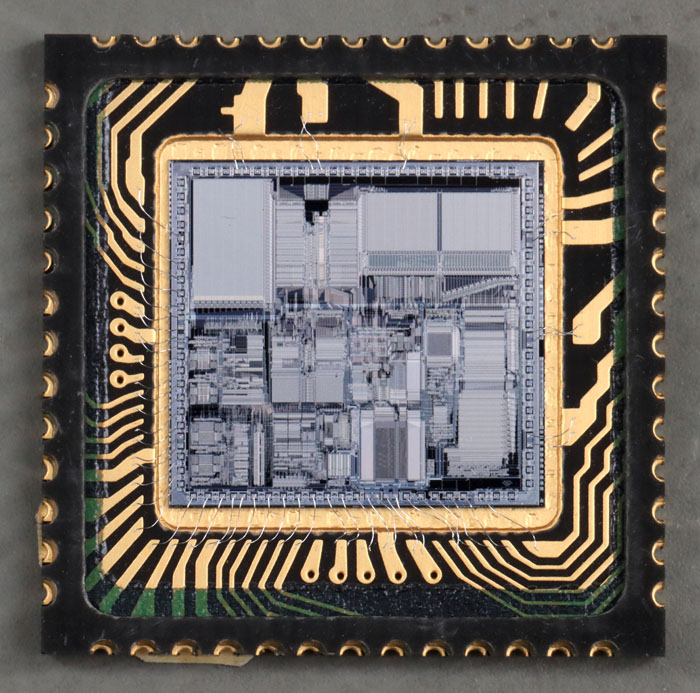

The XSP56001 is housed in a PGA-88 package. Alternatively, QFP-132 packages were also available. The metal surfaces on the underside could be used to mount capacitors, which would then stabilize the supply.

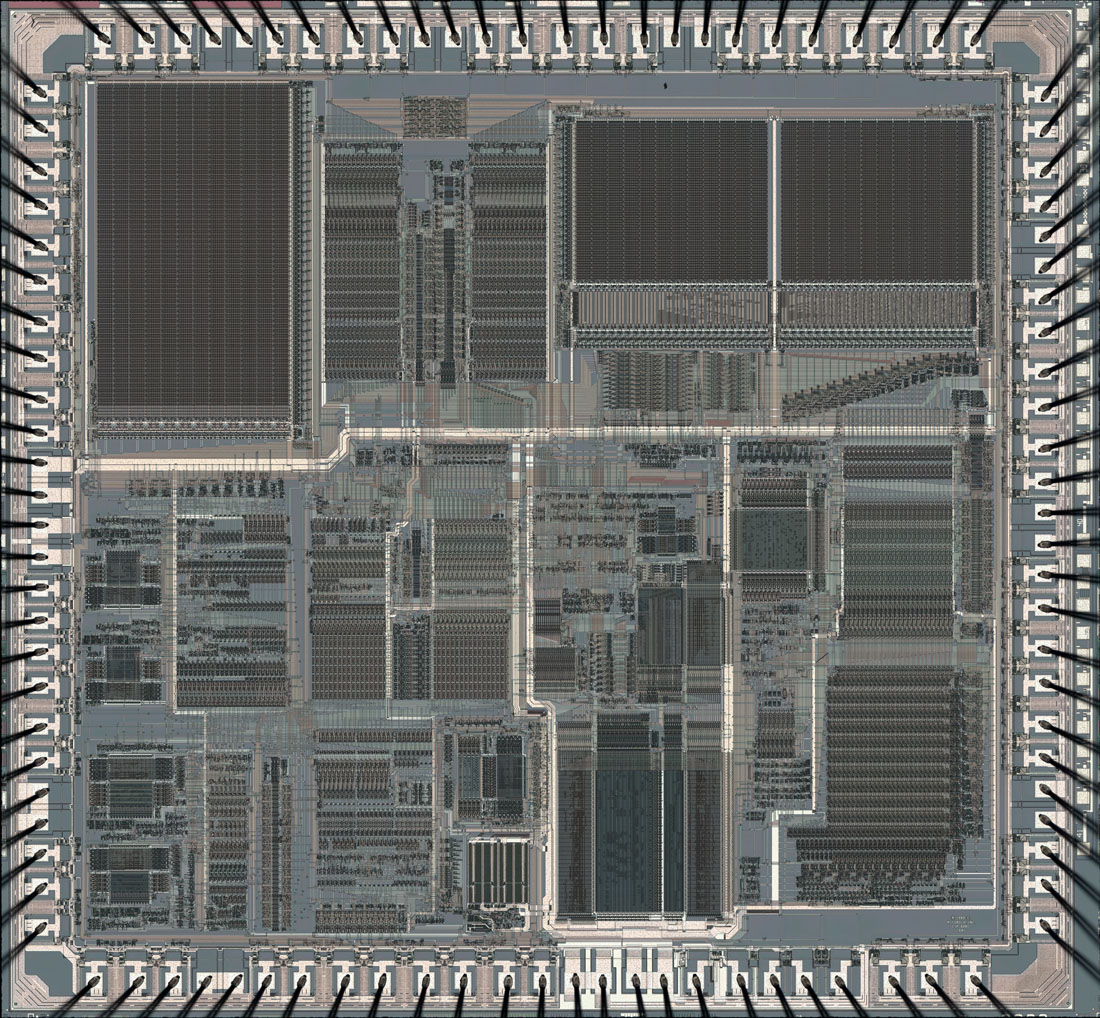

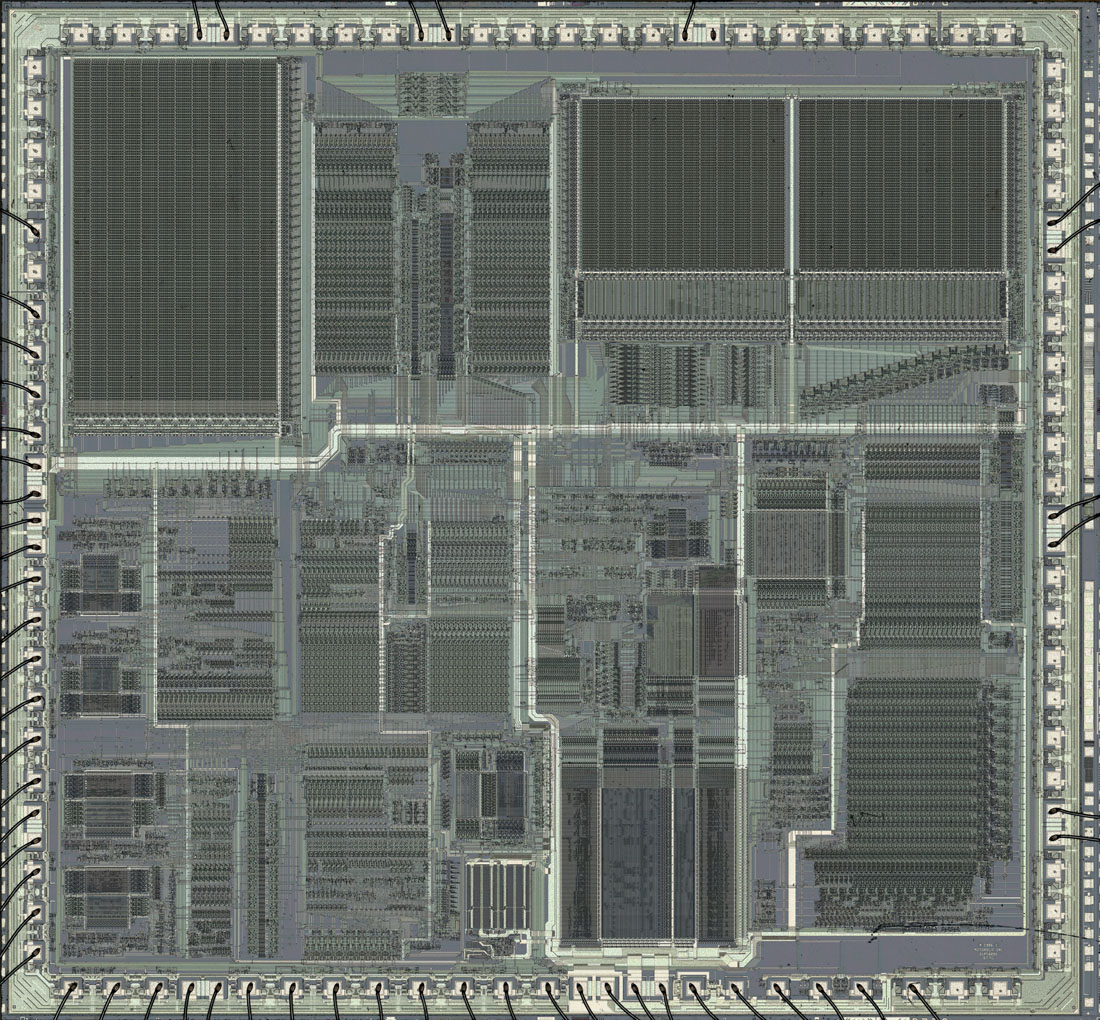

The dimensions of the die are 8,0mm x 7,4mm. The program ROM is located in the upper left corner. The RAM is located in the upper right corner. The slightly smaller memory area at the bottom edge contains the microcode that controls the function blocks of the DSP.

This image is also available in a higher resolution:

https://www.richis-lab.de/images/dsp/03x06XL.jpg (51MB)

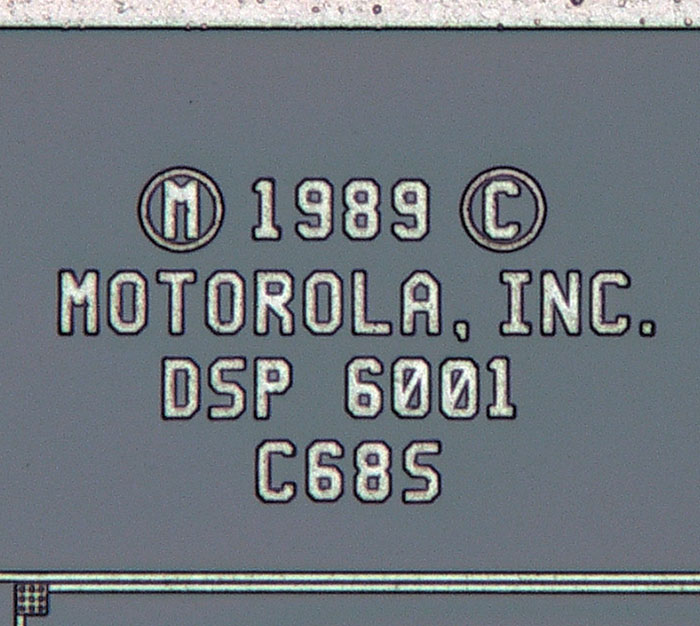

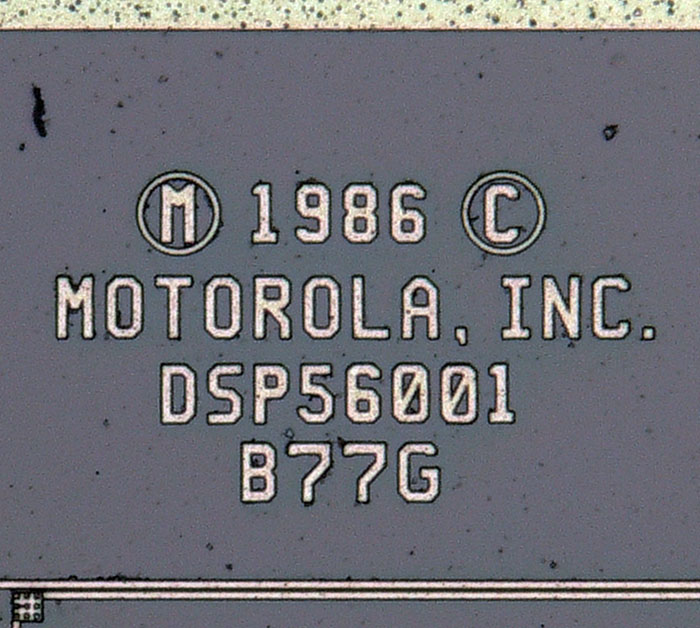

The design dates back to 1989. Interestingly, only the character string DSP 6001 is shown; the number 5 is missing. C68S indicates the mask revision.

A square is depicted in the metal layer in the lower left corner. These squares are often found on the die. They are probably preparations to make it easier to contact these potentials in case of troubleshooting.

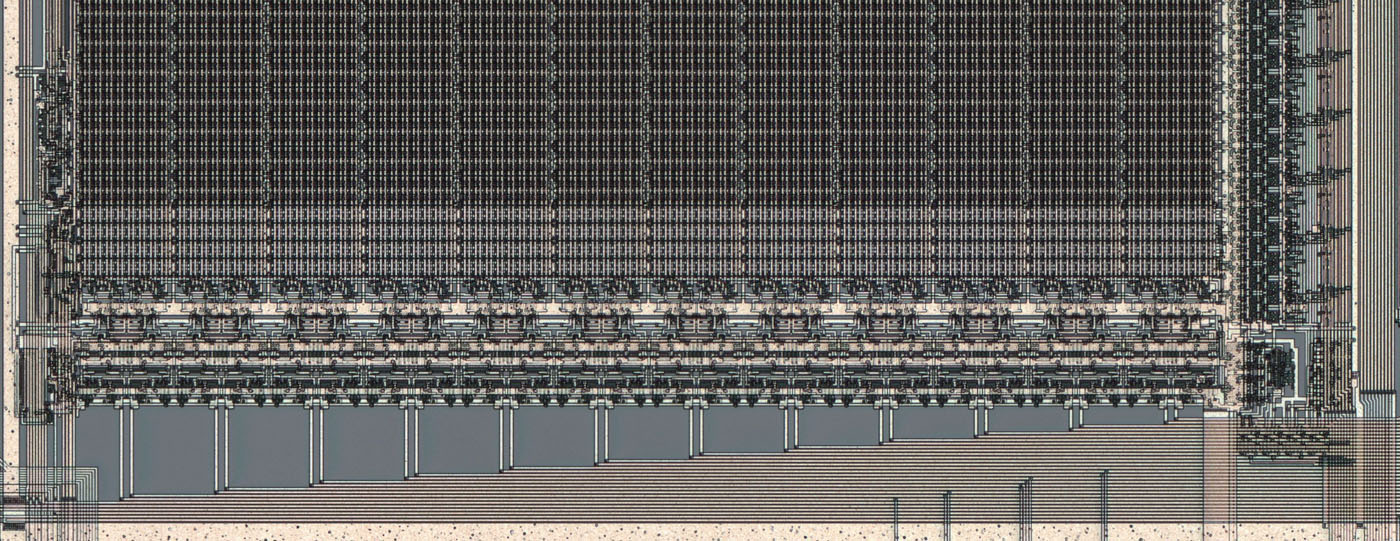

The boundary between the RAM and the boot ROM is clearly visible in the program memory. Apparently, the larger RAM memory cells were used and reconfigured as ROM cells. This approach wastes local silicon area, but allows the RAM's selection and readout circuits to be shared.

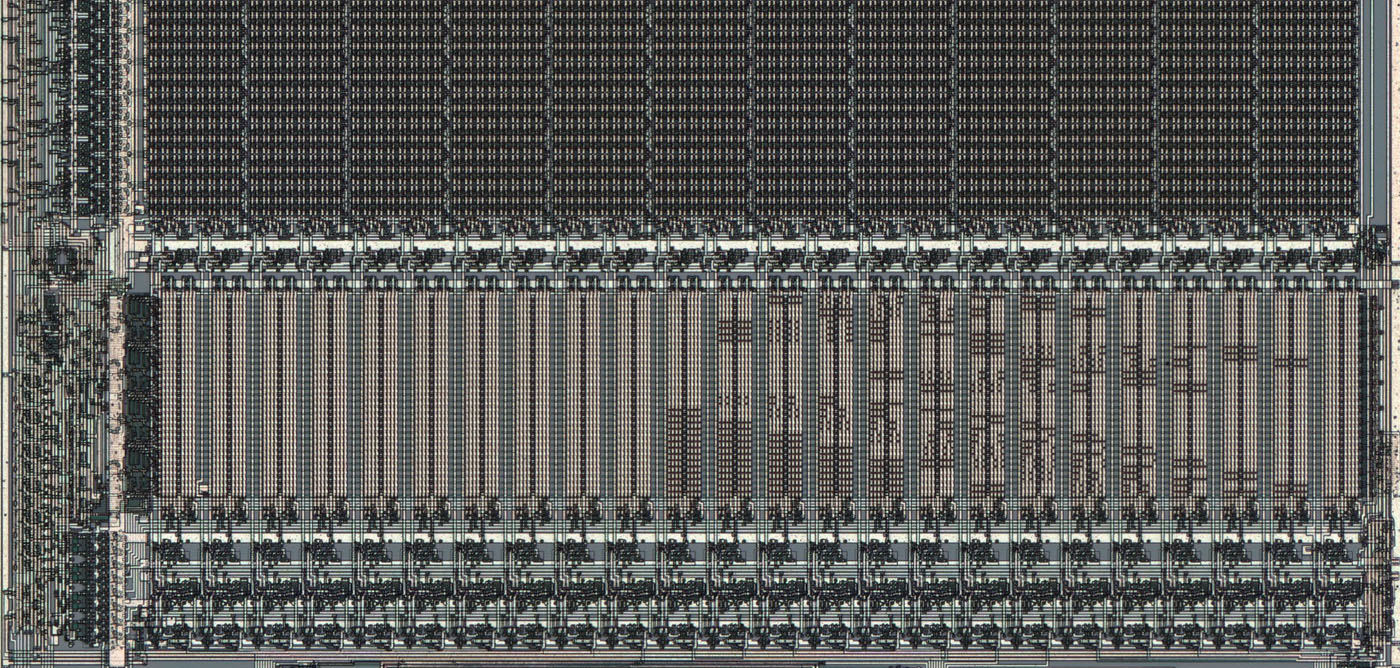

In contrast, optimized ROM areas have been integrated below the working memory. The contents are clearly recognizable.

Here you can see a development part of the DSP56001. The package only has 52 connections, not the 132 contacts that a DSP56001 in a QFP package usually has. Apparently, the data and address bus have been completely omitted.

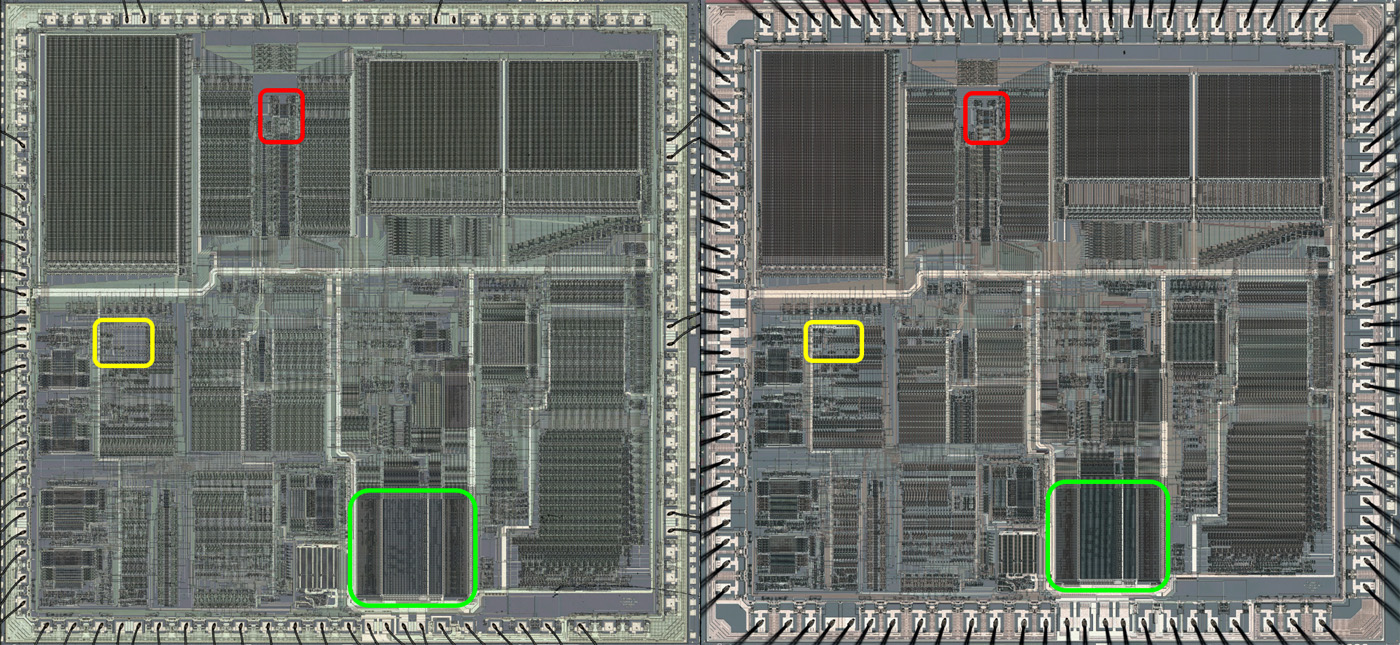

The dimensions of the die are 11,6mm x 10,7mm. It is thus significantly larger than the C68S revision (8,0mm x 7,4mm). Since the architecture appears to be fundamentally the same, the structure size has apparently been reduced. The 1987 IEEE publication “The Architecture and Applications of the Motorola DSP56000 Digital Signal Processor Family” states that a 1,5µm HCMOS process was used.

This image is also available in a higher resolution:

https://www.richis-lab.de/images/dsp/04x01XL.jpg (61MB)

The design dates back to 1986. It is revision B77G. Here, the designation DSP56001 is complete.

Major changes can be found in three areas. It is not surprising that the microcode has changed (green). A larger circuit section has been added to the left side of the die (yellow).

https://www.richis-lab.de/dsp03.htm