I am iterating options to generate accurate sine wave in terms of amplitude. Absolute frequency is not critical in this application.

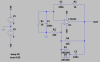

There are few options and the first in my mind was AGC controlled wien oscillator. The main factor is temperature. Since the AGC is based on diodes, the "accuracy" of the circuit below is not even on the right map.

Another option is to use AD9833 (or equivalent) waveform generator chip. There might be better options in terms of amplitude accuracy, but the chip in question looks like be able to keep amplitude within 0.3% between 25 and 50C.

In practice, generating square wave accurately (still talking about amplitude) might be the easiest. Then it is matter of filtering to get sine wave. (and this time taken into consideration temperature impact to resistors and capacitors).

The target is to have 0.1% accuracy. To get there I am expecting to have stable enough generator + calibration.

sw guy

Recent Posts

Recent Posts